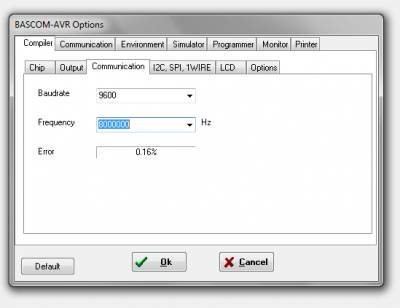

Здравствуйте. Я написал на асемблере следующую программу, но у Proteus пишеться при передачи байта :

PC=0x0032 [AVR USART] RX FRAME Error

У Proteus использовал VIRTUAL Terminal

Настроил его на 4800, 8-Data, 2 stop bits

Вот код программы :

.cseg

.Org 0

rjmp Begin

.Org 0x007

rjmp USART_RECEIVE

Begin:

ldi Temp,RamEnd

out SPL,Temp ;

;############ Инициализация USART, как передатчика ####################

;f=4000000MHz

;Глобально запретим прерывания, установим 8-ой бит регистра #

;SREG(регистр статуса) в 0.(Флаг I)

clI

;Установим Бодрейт 4800

;UBRR=(fosc/16*BAUD)-1; UBRR=(4000000/16*4800)-1=0x33

ldi Temp,0x33

out UBRRL,Temp

ldi Temp,0

out UBRRH,Temp

;разрешим передачу и прием

ldi Temp,(1<<RXEN)|(1<<TXEN)

out UCSRB,r16

;Установим формат посылки для USART:асинхронный режим(UMSEL=0) 8data, #

;2 stop bit

ldi Temp,(1<<USBS)|(3<<UCSZ0)

out UCSRC,Temp

sei

;#####################################################################

START:

;вывод r16 на LCD

rjmp start

USART_RECEIVE:

in r16,UDR

; у r16 принятый байт

RETI

|

Часовой пояс: UTC + 3 часа

Кто сейчас на форуме

Сейчас этот форум просматривают: нет зарегистрированных пользователей и гости: 7

Источник

Avr uart rx frame error

Перевод апноута AVR274 [1], который описывает софтовую реализацию однопроводного последовательного порта (UART). Протокол поддерживает полудуплексный обмен данными между 2 устройствами (передача в разных направлениях может происходить поочередно). Для реализации требуется только поддержка внешнего прерывания (external interrupt) на порте ввода/вывода I/O, и прерывание сравнения таймера (timer compare interrupt).

[1. Основные возможности и особенности программного UART]

• UART реализован программно

• Поддерживается полудуплексный обмен данными по одному проводу

• Используются прерывания

• Поддерживаются скорости передачи до 9600 на тактовой частоте ядра 1 МГц

• Описанный программный UART совместим с любым микроконтроллером AVR ® , который поддерживает внешнее прерывание (external interrupt, прерывание по изменению уровня на ножке GPIO) и имеет 8-битный таймер с поддержкой прерывания сравнения (timer compare interrupt).

Обмен данными с помощью физического протокола UART обычно осуществляется с использованием отдельных сигналов данных для приема и передачи (сигналы RX и TX). Однопроводный UART использует для обмена только одну сигнальную линию. Поэтому такой UART является идеальным для случаев, когда нужно реализовать недорогое решения для обмена данными, и не требуется высокая скорость и полнодуплексная передача. Этот апноут описывает софтовую (программную) реализацию однопроводного UART. Протокол поддерживает полудуплексный обмен между двумя устройствами AVR. Для реализации требуется только один вывод порта I/O, на котором поддерживается внешнее прерывание (external interrupt), и требуется прерывание сравнения таймера (timer compare interrupt).

[2. Теория: как это работает]

2.1. Фрейм (битовый кадр) UART

Протокол UART использует стандарт асинхронного последовательного обмена данными. Данные передаются последовательно, бит за битом, каждому биту отводится определенный отрезок времени. Эта реализация использует фрейм из 8 бит данных, 1 стартового бита и 2 стоповых бит, как это показано на рис. 2-1 (таким образом, каждый битовый кадр состоит из 11 элементарных битовых интервалов). Такой формат выбран потому, что на практике именно он чаще всего используется для передачи данных. Другие реализации могут использовать другие форматы фрейма, к примеру состоящие из 5..9 бит данных, 1 бита четности (parity, бит для определения наличия ошибки), и 1 стоповый бит. Конечно же, обе передающие стороны в обмене точка-точка должны быть настроены на один и тот же формат данных. Когда передачи нет, то сигнальная линия UART находится в состоянии лог. 1.

Рис. 2-1. Формат фрейма UART.

Рис. 2.2. Фрейм передачи последовательных данных для символа ASCII ‘a’ (код 0x61).

2.2. Передача данных

Передача инициализируется отправкой стартового бита, который всегда равен 0 (сигнальная линия притягивается к нижнему уровню). Приемник на другой стороне линии детектирует спад уровня на линии, и по этому событию может засинхронизироваться с передатчиком (синхронизация по времени требуется для корректного приема всех бит данных). Самый младший бит данных передается первым (см. рис. 2-2).

Выходы с открытым коллектором часто используются для такого управления линией данных, однако если сразу оба устройства на линии будут передавать в одно и то же время, то передатчик, передающий лог. 0, все равно будет притягивать линию к лог. 0, когда второй передатчик пытается передать бит 1. Чтобы обработать эту ситуацию, UART никогда не запускает передачу, когда он находится в режиме приема. Передатчик также проверяет сигнальную линию перед отправкой нового бита, чтобы убедиться, что её состояние не изменилось, когда передавался последний бит. Флаг ошибки устанавливается, если принят бит низкого уровня, когда последним передавался бит высокого уровня.

2.3. Прием данных

Прием запускается, когда был детектирован стартовый бит на линии. Затем состояние линии анализируется посередине каждого битового интервала фрейма, чтобы принять значение каждого бита информации. Таким образом, к примеру, первый бит данных выбирается после 1.5 периода бита после начала стартового бита. Эта реализация (для упрощения, и уменьшения загрузки ядра AVR) не использует тройную мажоритарную выборку для каждого бита (этот способ уточнения значения бита используется в большинстве аппаратно реализованных UART).

2.4. Битовая скорость передачи (Baud Rate)

Скорость обмена данными UART задается параметром baud rate. Его значение в этом случае эквивалентно количеству битовых интервалов, которые проходят за единицу времени. Так как во фрейме применяются стартовый и стоповые биты, то реальная скорость передачи данных получается несколько меньше (для нашего примера она равна 8/11 от значения baud rate). Приемник и передатчик должны быть настроены на использование одного и того же значения baud rate, иначе они не смогут засинхронизироваться по битам, и обмен данными не получится. Имеется стандартный ряд скоростей baud rate: 4800, 9600, 19200, 28800, 38400 и т. д.

2.5. События ошибки (Error Conditions)

В процессе передачи данных могут произойти ошибки разного вида. Если скорости baud rate слишком отличаются между двумя устройствами, то они будут рассинхронизированы. Поскольку baud rate зависит от таковой частоты ядра AVR, эта проблема может возникнуть, если реальная тактовая частота отличается от той, которая нужна. К примеру, если используется внутренний тактовый генератор (internal RC oscillator), то рекомендуется его откалибровать перед началом использования UART. Пожалуйста обратитесь к соответствующим апноутам, чтобы узнать, как калибровать внутренний RC-генератор.

Принятый байт данных сохраняется в однобайтовом буфере данных. Если принятые данные не были обработаны вовремя, до того как начался прием следующего байта, то буфер будет переполнен, и старые данные будут перезаписаны. Флаг переполнения будет установлен, если произойдет такая ошибка. В устранении такой ошибки может помочь снижение используемой скорости UART, либо увеличение размера буфера, тогда у основной программы будет больше времени, чтобы обработать принятые данные. Либо нужно вызывать процедуру проверки и обработки буфера чаще, с максимально возможной частотой.

Если шумовой импульс помех принудительно переведет линию сигнала в лог. 0, то AVR определит спад сигнала и начнет прием. Если детектировано начало стартового бита, но он оказался ненулевым, то AVR остановит прием и не сохранит никаких данных, но если импульс шума оказался длиннее нескольких циклов тактовой частоты, то будет принят и сохранен неправильный байт (который на самом деле никто не передавал).

Шум может также исказить фрейм и во время передачи. Так как состояние бита выбирается только один раз, то фрейм может быть принят с ошибкой, если импульс шума пришелся на момент считывания приемником состояния сигнальной линии. Для определения наличия таких ошибок может помочь добавление к фрейму UART бита четности (parity bit), при этом гарантированно могут быть зарегистрированы только одиночные ошибки фрейма.

Поскольку для работы UART используются прерывания, то основной код программы (код приложения, который выполняется в главном цикле main) может выполняться «параллельно», вместе с обменом UART. Имейте в виду, что поскольку AVR не поддерживает приоритетов прерываний, то другие активные источники прерываний могут повлиять на UART (к примеру, не будут точно вычисляться интервалы битов), и это может привести к ошибкам в обмене данными.

Рекомендуется использовать UART в обмене точка-точка, когда одно устройство является главным, другое подчиненным (так называемая конфигурация master/slave). Тогда slave будет передавать данные только тогда, когда их запросил master. Это предотвратит ситуации, когда оба устройства передают в одно и то же время. Если slave находится в состоянии ошибки, то он может сигнализировать об этом для master, если притянет сигнальную линию UART к лог. 0 на заданное время. Тогда будет установлен флаг ошибки master, и обмен будет продолжен только тогда, когда slave прекратит удерживать линию с состоянии лог. 0.

Прим. переводчика: схема обмена master/slave часто используется даже в физически полнодуплексных системах, когда для передачи и приема используются отдельные сигналы TX и RX. Это делается с целью упрощения логики протокола обмена, и позволяет проще синхронизировать высокоуровневое состояние обменивающихся данными устройств. В частности, принцип master/slave используется в последней версии протокола STK500, а также это основной принцип работы шины USB.

[3. Реализация]

Код, описываемый в этом апноуте, написан как драйвер, предназначенный для обмена данными через UART.

3.1. Установка скорости Baud Rate

Для генерации интервалов времени, используемых при выборке бит приема и при формировании интервалов передаваемых бит, используется прерывание сравнения содержимого таймера с предустановленным значением (timer compare interrupt). Таймер настраивается в режим очистки при совпадении сравнения, режим Clear Timer on Compare (CTC), и на это событие настраивается прерывание. Это прерывание срабатывает, когда содержимое счетчика таймера уравнивается с содержимым регистра сравнения (output compare register). Время между каждым таким прерыванием зависит от системной тактовой частоты ядра, настройки предделителя тактовой частоты таймера (коэффициента деления прескалера), и от значения, записанного в регистр сравнения (compare register), как это показано в Формуле 3-1. Установка compare value в значение 10 приведет к генерации длительности между прерываниями в 11 тиков. Настройки скорости UART (Baud rate) устанавливаются в хедере UART, файле single_wire_UART.h.

Формула 3-1. Вычисление скорости передачи (Baud Rate).

Формула 3-2. Вычисление значения для регистра совпадения.

Пояснения к формулам: «System Clock» означает тактовую частоту системы в Гц. «One Period Compare Setting» — значение, записанное в регистр сравнения таймера (output compare register). «Timer Prescaler» — коэффициент деления прескалера. «One Period Compare Setting» — значение для регистра сравнения, которое определяет период срабатывания обработчика таймера, что задает длительность бита UART.

Таблица 3-1. Установка периода бита UART для частоты тактового генератора 1, 2, 4 и 8 МГц.

| Baud Rate (bps) |

1 МГц | 2 МГц | ||||

| OPS | PS | Error | OPS | PS | Error | |

| 4800 | 207 | 1 | -0.16% | 51 | 8 | -0.16% |

| 9600 | 103 | 1 | -0.16% | 207 | 1 | -0.16% |

| 19200 | не реализовано | 103 | 1 | -0.16% | ||

| 4 МГц | 8 МГц | |||||

| 4800 | 103 | 8 | -0.16% | 207 | 8 | -0.16% |

| 9600 | 51 | 8 | -0.16% | 103 | 8 | -0.16% |

| 19200 | 207 | 1 | -0.16% | 51 | 8 | -0.16% |

| 28800 | 138 | 1 | 0.08% | 34 | 8 | 0.82% |

| 38400 | 103 | 1 | -0.16% | 207 | 1 | -0.16% |

Пояснения к таблице: OPS означает One Period Settings (One Period Compare Settings, значение регистра сравнения таймера, от которого зависит длительность между срабатываниями прерываний таймера и вызовами обработчика Timer_Compare_SW_UART_ISR), PS означает Prescaler Setting (коэффициент деления прескалера), Error означает погрешность полученной реальной скорости UART в процентах (по отношению к требуемой стандартной скорости).

В таблице 3-1 показаны установки таймера для некоторых стандартных скоростей передачи, а также получающаяся погрешность установленной скорости. Погрешность установки скорости скорости (Error) вычисляется по формуле 3-3.

Формула 3-3. Вычисление ошибки установки скорости UART.

Пояснения к формуле: Error[%] — погрешность установки скорости, насколько скорость отличается от стандартной. Baud RateClosest Match — скорость UART по стандарту. Baud Rate — полученная по формуле 3-1 реальная скорость.

Имейте в виду, что максимальная скорость UART, которую реально можно получить, зависит от тактовой частоты ядра AVR и от его загруженности другими вычислениями (кодом, который должен выполняться в других прерываниях и в главном цикле main). Если превысить эту скорость, то UART перестанет работать, и основная программа также практически перестанет выполнять свои функции. Так происходит потому, что выполнение обработчика прерывания таймера не успеет завершиться, как таймер снова досчитает до значения регистра сравнения, и произойдет новое прерывание. Максимально допустимое количество циклов, которое может быть выполнено в прерывании compare interrupt, составляет около 100..110, и зависит от настроек компилятора. На практике использование тактовой частоты ядра 1 МГц дает максимально возможную скорость UART около 10000 бит/сек (бод). При этой скорости все время выполнения CPU будет израсходовано только на обработку UART, и на остальные задачи практически циклов не останется. Основной код приложения (действия, которые прокручиваются в основном цикле main) должен иметь некоторое время на обработку принятых данных до того, как поступит новый битовый фрейм, иначе произойдет ошибка переполнения, и некоторые данные на приеме будут потеряны. Поэтому рекомендуется установить скорость обмена UART несколько ниже предельно допустимой для заданной частоты ядра, в зависимости от требований к коду основного приложения.

Формула 3-4. Максимально допустимая скорость обмена программного UART.

Пояснения к формуле: Baud Rate — полученная по формуле 3-1 реальная скорость. System Clock — тактовая частота, на которой работает AVR. Maximum Cycles in Compare Interrupt — максимальная длительность выполнения обработчика прерывания сравнения таймера в циклах ядра.

3.2. Аппаратура, на которой реализован UART (Hardware)

В этой реализации шина данных UART разработана в расчете на использование внешнего верхнего нагрузочного резистора (pull-up). Таким образом, должны использоваться ножки ввода вывода (I/O, GPIO) с открытым коллектором (открытым стоком). Дополнительно нужно использовать вешнее прерывания для детектирования начала приходящего битового фрейма.

Типичное значение нагрузочного резистора pull-up микроконтроллера AVR составляет 15..40k?. Когда отправляется бит с высоким логическим уровнем, или когда происходит прием, то порт AVR для данных UART находится в третьем состоянии (настроен как вход с отключенным внутренним нагрузочным резистором). Бит с низким логическим уровнем отправляется путем конфигурирования порта как выхода с выведенным в порт лог. 0.

Если требуется обмен данными по физическому каналу стандарта RS-232, то необходимо приведение уровня сигнала UART к значениям -12..-15V (соответствует лог. 1) и +12..+15V (соответствует лог. 0). Для этого нужна специальная схема, которая делает инверсию, и приводит уровни сигнала к нужным значениям. Например, можно использовать специальный чип интерфейса MAX232 компании Maxim. Он работает от одного напряжения питания 5V, и имеет встроенный преобразователь напряжения DC/DC, чтобы генерировать стандартные уровни RS-232.

Прим. переводчика: можно также использовать преобразователь с гальванической изоляцией на основе оптронов [2].

3.3. Регистр состояния (Status register)

Регистр состояния однопроводного UART содержит следующие 4 флага: SW_UART_TX_BUFFER_FULL, SW_UART_RX_BUFFER_FULL, SW_UART_RX_BUFFER_OVERFLOW, SW_UART_FRAME_ERROR.

SW_UART_TX_BUFFER_FULL устанавливается, если данные TX готовы к передаче. Этот флаг должен быть обнулен, когда вызывается функция SW_UART_transmit.

SW_UART_RX_BUFFER_FULL устанавливается, если в приемном буфере есть необработанные принятые данные. Этот флаг должен установиться в лог. 1, когда вызывается функция SW_UART_Receive.

SW_UART_RX_BUFFER_OVERFLOW устанавливается, когда приходящие данные потеряны из-за переполнения буфера приема (новый прием начался, но ранее принятые данные не были обработаны).

SW_UART_FRAME_ERROR устанавливается, если неожиданно обнаружена лог. 1 в стартовом бите (на самом деле стартовый бит должен быть всегда нулевым), или если обнаружен лог. 0 в стоповом бите (стоповый бит должен быть всегда в лог. 1). Также устанавливается, когда при передаче считанный бит отличается от того, что был передан.

Чтобы уменьшить размер кода, регистр состояния может быть помещен в регистр GPIO, если это доступно (это нельзя сделать для ATmega32).

3.4. Счетчик UART

Переменная счетчика используется в коде драйвера UART, чтобы управлять состоянием, и какой бит принимается/передается через UART. UART переходит в состояние ожидания, когда значение счетчика равно 0. Значение счетчика является четным при передаче и нечетным при приеме, как показано на рис. 3-1.

Рис. 3-1. Значения счетчика UART.

3.5. Функции UART

Драйвер состоит из трех глобальных функций (описание функций см. далее):

SW_UART_status является глобальной переменной, которая удерживает флаги состояния UART (см. раздел 3.3). Макросы SET_FLAG, CLEAR_FLAG и READ_FLAG, определенные в хедере single_wire_UART.h, можно использовать для получения доступа к флагам.

В реализации UART используются также следующие обработчики прерывания:

Перед тем, как данные могут быть приняты или переданы через UART, он должен быть разрешен вызовом функции SW_UART_Enable. Он переводит ножку UART в состояние ожидания (при этом на выходе получается высокий уровень благодаря внешнему pull-up резистору). Регистр состояния и счетчик очищаются, так что исходящие передачи, если они работали, будут остановлены. Запрет внешнего прерывания и прерывания таймера остановят работу UART.

Рис. 3-2. Алгоритм работы функции SW_UART_Enable().

Функция SW_UART_Transmit() получает 1 байт в качестве параметра и добавляет этот байт в буфер передачи. Когда вызывается эта функция, то флаг SW_UART_TX_BUFFER_FULL должен быть очищен (его должен очищать внешний код передачи байт), иначе зарегистрируется потеря данных. Если передача данных не происходит, когда вызывается эта функция, то запустится новая передача путем отправки стартового нулевого бита и разрешения работы прерывания таймера.

Рис. 3-3. Алгоритм работы функции SW_UART_Transmit().

Эта функция возвратит принятый байт в переменной Rx_data. Перед вызовом этой функции должен быть проверен флаг UART_RX_BUFFER_FULL, чтобы убедиться, что в буфере Rx_data есть верные данные. При приеме нескольких байт, следующих друг за другом, очень важно вызвать эту функцию до приема следующего байта, иначе буфер приема будет переполнен и данные потеряются.

Рис. 3-4. Алгоритм работы функции SW_UART_Receive().

Обработчик внешнего прерывания External_SW_UART_ISR() будет вызван при детектировании спада уровня сигнала данных UART, когда нет выполняющихся операций передачи или приема. Обработчик проверяет, что ножка вывода данных UART находится в лог. 0. Если это не так, то прием не запускается. После начала приема фрейма запрещаются дальнейшие внешние прерывания, так что последующие спады уровня не вызовут повторного срабатывания внешнего прерывания с новым вызовом обработчика External_SW_UART_ISR. Таким образом, External_SW_UART_ISR используется только для детектирования стартового бита фрейма.

Рис. 3-5. Алгоритм работы обработчика прерывания External_SW_UART_ISR().

Обработчик прерывания по совпадению таймера Timer_Compare_SW_UART_ISR() (моменты срабатывания таймера показаны стрелочками на рис. 3-1) управляет обработкой передачи и приема битового фрейма. Он вызывается автоматически, когда значение регистра сравнения (output compare) уравнивается со значением аппаратного счетчика таймера, и когда разрешено прерывание таймера. На передаче счетчик UART начинает считать с четного значения (2, 4, . ), а на приеме с нечетного значения (1, 3, . Не путайте счетчик UART со аппаратным счетчиком таймера). Обработчики приема (рис. 3-8) и передачи (рис. 3-7) реализованы напрямую в обработчике прерывания таймера. Пожалуйста обратитесь к рис. 3-1 для подробностей по поводу разных значений счетчика.

Рис. 3-6. Алгоритм работы обработчика прерывания Timer_Compare_SW_UART_ISR().

Рис. 3-7. Обработчик передачи UART_Transmit_Handler().

Рис. 3-8. Обработчик приема UART Receive Handler().

3.6. Программа примера

Модуль main.c содержит код программы примера для тестирования софтового однопроводного UART. Он принимает данные в массив байт, и передает эти данные обратно, когда массив заполнится, или когда будет принят символ возврата каретки ‘n’.

3.7. Размер кода

При компиляции с использованием IAR® EWAVR 4.21A, с включенной оптимизацией по скорости по максимуму, размер кода драйвера UART занимает около 500 байт.

[4. Указания по быстрому старту]

Источник

Adblock

detector

-

proteus

-

avr

-

max485

-

uaert

-

rx frame error

-

Ответить

-

Создать новую тему

Рекомендуемые сообщения

Присоединяйтесь к обсуждению

Вы можете написать сейчас и зарегистрироваться позже.

Если у вас есть аккаунт, авторизуйтесь, чтобы опубликовать от имени своего аккаунта.

Примечание: Ваш пост будет проверен модератором, прежде чем станет видимым.

-

Последние посетители

0 пользователей онлайн

- Ни одного зарегистрированного пользователя не просматривает данную страницу

-

Сообщения

-

Автор

Black-мур · Опубликовано 6 минут назад

Вряд ли, это нормальная реакция нормального человека, способного защищаться. Но меня, к примеру(только с меня пример брать не нужно ) только за намёк-упоминание об этом иногда в бане запирают. Хорошо ещё, что находятся адекватные, трезвомыслящие люди и выпускают.

-

Автор

IvanTikh · Опубликовано 10 минут назад

вот нарисовал еще, это 2 секции первички на каркасе(как мы на него смотрим, и как расположились выводы обмотки), как соединить правильней, лучше, и т.д., для триода se? 2ой вывод с каким?

-

-

Автор

Alex Ferrum · Опубликовано 17 минут назад

@IMXO и что, что я этот вопрос задавал. Если уж собрались симулировать схемы нужно реальные параметры задавать, а не такие что при которых на 60-120 ваттном двигателе рассеиваться аж 2 киловатта.

Насчёт эдс самоиндукции, так она никогда не вносила значимый вклад в нагрев транзисторов, у меня мосты с двигателями никогда особо не грелись, особенно закрытые транзисторы. Ну а вы наслушавшись всякого детского сада и НЕКОРРЕКТНО симулировав схемы получаете фантастические результаты.

-

-

-

Автор

ВасяШпунт · Опубликовано 20 минут назад

Здравствуйте уважаемые!

Оплатил я 2 шт. ТВЗ 80 Ростову «66 д.0.8 1300 д.0.281300 д.0.28 33 +33 д.0.8. 66+33 =8 ом 66+33+33=16 ом.» (они ближе). Пока едут решил шасси доделать, наждак и грунтовка — вот результат. Хочу вишнёвый металлик.

-

-

Похожий контент

-

0

Автор

Deerael

Started 11 часов назад -

-

-

-

1

Автор

lollik68

Started 11 ноября, 2022

-

|

Blekzet 4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

||||

|

1 |

||||

|

18.11.2019, 15:03. Показов 4005. Ответов 18 Метки нет (Все метки)

Собственно у меня вообще отказываются работать прерывания с USART

Вот такой простенький код, не хочет работать (собираю на AtmelStudio 7, симулирую в протеусе 7.7) Добавлено через 36 минут

__________________

0 |

|

liv Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

||||||||

|

18.11.2019, 15:13 |

2 |

|||||||

|

Blekzet, два вопроса:

лишнее. Вы же работаете по прерыванию, а не по опросу.

0 |

|

Blekzet 4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

||||

|

18.11.2019, 16:20 [ТС] |

3 |

|||

|

да там такая же история, тишина

Добавлено через 1 минуту

0 |

|

liv Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

||||

|

18.11.2019, 16:22 |

4 |

|||

|

Ничего не надо делать.

0 |

|

Blekzet 4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

||||

|

18.11.2019, 16:24 [ТС] |

5 |

|||

|

liv, тишина….

0 |

|

Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

|

|

18.11.2019, 16:25 |

6 |

|

Blekzet, а запретить прерывания по передаче не пробовал?

0 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 16:25 [ТС] |

7 |

|

liv, так тоже тишина

0 |

|

Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

|

|

18.11.2019, 16:27 |

8 |

|

Blekzet, еще момент, рассказывай, какие фьюзы

0 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 16:27 [ТС] |

9 |

|

liv, 1111

0 |

|

Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

|

|

18.11.2019, 16:29 |

10 |

|

Хотя, если по опросу работает… Хм, интересненько… Добавлено через 1 минуту

1111 Расшифруй. Я Протеусом не пользуюсь. Работаю всегда только с железом

0 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 16:38 [ТС] |

11 |

|

liv, Ext. Crystal/Resonator High Freq.; Start-up time: 16K CK + 64 ms; [CKSEL=1111 SUT=11] Добавлено через 6 минут

0 |

|

Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

|

|

18.11.2019, 16:39 |

12 |

|

А в программе 8 МГц

0 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 16:42 [ТС] |

13 |

|

liv, разве? Я вроде все по методичке делал…

0 |

|

liv Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

||||

|

18.11.2019, 16:45 |

14 |

|||

|

И даже не 8 МГц, а 800КГц !!!

А не, обознался… 8 МГц Добавлено через 2 минуты

0 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 16:55 [ТС] |

15 |

|

liv, та же тишина… Добавлено через 6 минут

0 |

|

Модератор 5107 / 4538 / 854 Регистрация: 07.10.2015 Сообщений: 9,462 |

|

|

18.11.2019, 17:00 |

16 |

|

РешениеBlekzet, так все-таки, частота-то какая? 8 или 16МГц? Добавлено через 2 минуты

1 |

|

4 / 4 / 0 Регистрация: 21.12.2015 Сообщений: 195 |

|

|

18.11.2019, 17:00 [ТС] |

17 |

|

liv, 8, да Добавлено через 48 секунд

0 |

|

BadNews_13 0 / 0 / 0 Регистрация: 11.01.2020 Сообщений: 2 |

||||||||

|

11.01.2020, 20:53 |

18 |

|||||||

|

Здравствуйте! Помогите понять как работают прерывания в USART. Пишу код в Atmel Studio 7 для Atmega328p. В функции putch() я отправляю байты в массив и разрешаю прерывание по опустошению регистра UDR. Для теста отправляю в putch() переменную, которая увеличивается на 1 в бесконечном цикле. Результат: Отправляется корректно только первые два байта, затем начинает проскакивать по десятку байтов и шлет например 15-й, а затем 28-й и т.д., но в какой-то момент (начиная с 133 байта) начинают приходить последовательные байты. Проверял в протеусе. Дебажил в Atmel Studio — тот же результат. После 2-го байта прекращает заходить в прерывание (флаг опустошения регистра UDR не поднимается) UCSRA = 0 , а UCSRB = -8 (как так?). Но до 133 цикла я не дощелкал. Ниже приведен код:

как скрины добавлять еще не разобрался, так что результат пока так покажу: 000001 20:14:55.746 00 01 1C 38 55 71 85 86 87 88 89 8A 8B 8C 8D 8E …8Uq…†‡€‰Љ‹ЊЌЋ PS: Ожидание в цикле while (как в большинстве примеров) пока не освободиться регистр UDR работает без пропусков, но надо же делать как правильно, а не как будто это единственная задача контроллера. PPS: предлагаю высказывания типа «Зачем мучиться? лучше купить готовое решение» прировнять к нецензурной лексике и наказывать баном.

0 |

|

0 / 0 / 0 Регистрация: 11.01.2020 Сообщений: 2 |

|

|

12.01.2020, 19:09 |

19 |

|

У меня максимальный размер буфера (TX_BUFFER_SIZE) равен 128. Соответственно когда он заполняется из-за того, что не попадаем в прерывание по опустошению UDR, тогда начинает работать цикл while в функции putch(), давая задержку по времени. Благодаря этой задержке начинают успевать улетать данные из UDR, и опять выполняется прерывание по опустошения, и как следствие получилась последовательная передача байт через ожидание в цикле (способ от которого нужно уйти). Только что нашел ошибку: Когда UDR занят, то байты складываю в массив. А когда мы наконец попадаем в прерывание, то в UDR кладется последний байт из массива, а не следующий после последнего отправленного . Вот и теряется по 25 байтов (пока UDR опустеет и поднимется флаг моя программа успевает сделать примерно 25 циклов). Но самые первые два байта нормально улетают. Возможно первый проваливается в UDR, а второй в сдвиговый регистр перед ним, поэтому сохраняется последовательность. Но это предположение. PPS: предлагаю высказывания типа «Зачем мучиться? лучше купить готовое решение» прировнять к нецензурной лексике и наказывать баном.

0 |

|

Проблемы с UART. Frame error. |

||||||||

|

||||||||

|

||||||||

|

||||||||

|

||||||||

|

Avr usart rx frame error

UART (USART) обычно нужен для организации взаимодействия с внешним миром — чтобы передать микроконтроллеру какие-то команды и забрать у него данные. Или как минимум для отладки — чтобы понять, что происходит с Вашей программой.

Примечание: аббревиатура USART переводится как Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART), т. е. последовательный порт может работать как синхронный (по внешнему тактовому сигналу), так и асинхронный (аппаратно формировать посылки бит по интервалам времени).

Запуск USART обычно состоит из следующих простых действий:

1. Создать буферы приема и передачи (типа FIFO, обычно кольцевые).

2. Написать код инициализации USART.

3. Написать обработчик прерывания приема символа из USART.

4. Написать обработчик передачи USART.

5. Перенаправление вывода printf в USART.

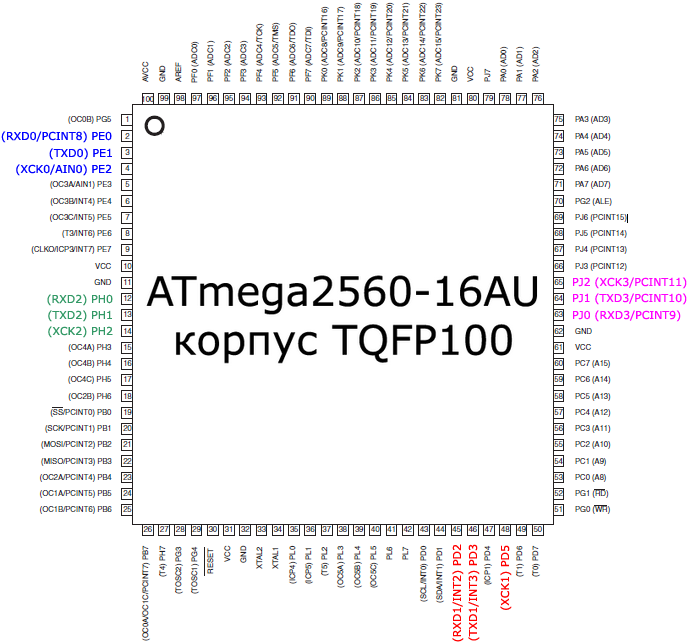

Рассмотрим каждую из этих операций. Все, что написано далее, может относиться во многом не только к микроконтроллеру ATmega2560, но и к любому AVR, который имеет на борту аппаратуру USART (или UART).

[1. Буферы приема и передачи USART]

Буферы приема и передачи нужны для того, чтобы упорядочить потоки входных и выходных данных в программе. На приеме обработчик прерывания нужен потому, что символ (байт) может прийти из внешнего мира асинхронно, т. е. в любой момент времени. Аппаратный буфер USART у AVR очень мал — всего лишь 2 байта.

Примечание: в микроконтроллере ATmega2560 буфер приема читается через регистр UDRn, где буква n меняется на номер используемого порта 0, 1, 2 или 3 (у ATmega2560 целых 4 последовательных порта USART: USART0, USART1, USART2 и USART3).

Следовательно, чтобы не потерять пришедшие данные, нужно как можно быстрее считать из буфера и обработать принятый байт, иначе следующий поступивший байт может затереть только что пришедший байт, и этот предыдущий байт может быть потерян (так называемый RX overrun).

Для быстрого считывания поступившего байта обычно используется обработчик прерывания приема USART. Буфер считывается из регистра UDRn и помещается в буфер, откуда он потом может быть выбран основной программой. Возникает вопрос: так зачем все-таки нужен буфер, почему нельзя сразу в обработчике прерывания предпринять какие-то действия, и обойтись без дополнительного буфера? Ответ прост: да, можно так сделать, но только для самых простых случаев, когда обработка байта не займет много времени, и когда не нужно производить дополнительных действий. Например, не получится обойтись без программного буфера, если поток входных данных соответствует какому-то протоколу, нельзя обрабатывать каждый байт по отдельности, нужно отслеживать таймауты в потоке входных байт и т. п. Такие сложные действия иногда нельзя возложить на обработчик прерывания, потому что они займут слишком много времени, и это повлияет на работоспособность всей программы в целом. Таким образом, обработчик приема может просто поместить принятый в буфер байт и быстро завершить свою работу. Опустошать буфер приема может основная программа, которая может быть довольно сложной и медлительной.

Буфер для передачи делают потому, что в одном действии программы обычно надо передать через USART не один байт, а сразу несколько. Например, нужно вывести приветствие printf(«Hello World!»), или какое-то диагностическое сообщение, состоящее из нескольких байт. Но USART может передавать только по одному байту, через аппаратный буфер регистра UDRn. Если аппаратный буфер не опустошился, т. е. если USART не успел еще передать только что записанный в UDRn байт, то нельзя в цикле без задержки писать все символы передаваемой строки в UDRn, иначе произойдет потеря данных при передаче (TX overrun). Чтобы не было непроизводительных потерь процессорного времени на циклы ожидания, делается программный буфер достаточного размера, куда программа может без задержки поместить все данные, которые надо передать. Опустошаться буфер передачи будет по одному байту — в основной программе и/или в обработчике прерывания опустошения буфера, по мере того, как аппаратура USART будет готова передать очередной байт.

Вот пример организации буферов передачи и приема USART (подробнее про кольцевые буферы см. [1]):

В этом примере размеры буферов приема и передачи выбраны одинаковыми, но это совершенно не обязательно. К размеру буферов передачи и приема есть два простых требования, которые зависят от того, как работает Ваша программа. Во-первых, размер буфера должен быть достаточно велик, чтобы он никогда не переполнялся. Это означает, что на приеме Вы всегда успеваете забрать и обработать поступающие данные до того, как буфер переполнится (т. е. данные поступают всегда медленнее, чем Вы их читаете и обрабатываете). Аналогично на передаче Вы не должны писать в буфер передачи слишком часто, буфер передачи должен успевать опустошаться кодом поддержки аппаратуры передачи USART. Во-вторых, есть требование, которое вытекает из примененного принципа обработки кольцевого буфера [1]: размер буфера должен быть равен степени 2, т. е. 2, 4, 8, 16, 32, 64 и т. д. Это требование не обязательное, если Вы согласны усложнить обработку индексов буфера, но имейте в виду, что усложнение кода обработки индексов замедлит обработку приема и передачи, и иногда такое замедление может оказаться недопустимым.

Таким образом, чем больше буфер, тем лучше. Но нельзя увеличивать буфер бесконечно, потому что у микроконтроллера ресурсы ограничены, и нужно всегда искать разумный компромисс.

[2. Код инициализации USART]

В этом примере будем настраивать USART0, который используется в плате Arduino Mega 2560 [2] в качестве стандартного канала обмена с компьютером через USB. Параметры для настройки 115200 bps, 8 бит данных, без четности, 1 стоп-бит.

После сброса (перезагрузки) все регистры AVR, в том числе и регистры, которые устанавливаются в исходное состояние. Чтобы USART заработал как нужно, необходимо настроить биты его регистров (подробное описание регистров см. во врезке «Справочная информация по USART ATmega2560»):

UCSR0A.U2Xn бит двойной скорости передачи.

UCSR0A.MPCMn бит включения функции мультипроцессорного обмена.

Обе эти функции не нужны, поэтому в UCSR0A нужно записать 0.

Примечание: можно было бы этого и не делать, потому что после сброса регистр UCSR0A сам автоматически обнуляется. Однако сброс регистра UCSR0A в программе не помешает, он будет явно показывать, какая настройка порта USART используется.

UCSR0B.RXCIE0 разрешение прерывания приема. Мы будем использовать обработчик прерывания по наличию в буфере приема данных, поэтому этот бит нужно установить в 1.

UCSR0B.RXEN0 разрешение работы приемника, сюда нужно записать 1.

UCSR0B.TXEN0 разрешение работы передатчика, сюда нужно записать 1.

UCSR0B.UCSZ02 это один из 3 бит, который настраивает количество бит данных во фрейме. У нас размер данных фрейма 8 бит, по таблице 22-7 значение этого бита должно быть равно 0.

Остальные биты не нужны, поэтому они будут сброшены.

UCSR0C.UMSEL01 и UMSEL00 эти биты определяют режим работы USART. Нас интересует асинхронный режим, по таблице 22-4 значение этих бит должно быть нулевое.

UCSR0C.UPM01 и UPM00 эти биты определяют контроль четности. Нам он не нужен, поэтому по таблице 22-5 значение этих бит будет нулевое.

UCSR0C.USBS0 бит количества стоп-битов фрейма. У нас 1 стоп-бит, поэтому согласно таблице 22-6 значение этого бита нулевое.

UCSR0C.UCSZ00 и UCSZ01 эти биты совместно с битом UCSR0B.UCSZ02 определяют количество бит данных во фрейме. По таблице 22-7 значение бит UCSZ01 и UCSZ00 должно быть 11.

UCSR0C.UCPOL0 этот бит работает только в синхронном режиме, поэтому должен быть сброшен в 0.

Следовательно, в регистре UCSR0C нужно установить только биты UCSZ01 и UCSZ00:

UBRR0H , UBRR0L . Для этих регистров нужно по формуле рассчитать настройки для скорости (это 12-битный регистр UBRR0, доступ к которому дает пара регистров UBRR0H:UBRR0L). Поскольку у нас асинхронный режим, нет включенной двойной скорости, то наша формула будет следующей (см. таблицу 22-1):

16000000

UBRR0 = —————- — 1

16 * 115200

Получается, что значение для UBRR0 должно быть 7.68. Это дробное число, и его конечно же записать в регистры, поэтому число нужно округлить до ближайшего целого, получится 8.

Примечание: можно было бы воспользоваться таблицей 22-12, где есть готовое вычисленное значение UBRR для скорости 115.2K. Как следует из таблицы, для режима двойной скорости настройка получится точнее, в этом случае нужно записать в UBRR0 значение 16, и бит U2X0 в регистре UCSR0A нужно установить в 1:

Несмотря на то, что на двойной скорости настройка получается точнее, все равно не факт, что это будет работать лучше, потому что оцифровка бит RXD будет осуществляться не по 16 выборкам, а по 8 (см. подробное описание работы приемника во врезке «Справочная информация по USART ATmega2560»).

Примечание: после того, как будет разрешен приемник и передатчик установкой бит RXEN0 и TXEN0 соответственно, функционирование портов ввода/вывода PE0 и PE1 будет автоматически переназначено. Теперь они будут работать как вход приемника и выход передатчика USART.

[3. Обработчик прерывания приема USART]

Обработчик прерывания приема должен выполнять простую задачу: читать регистр UDR0, и писать его значение в кольцевой буфер.

Примечание: константу USART0_RX_vect можно подсмотреть в файле avrincludeavriomxx0_1.h тулчейна (это может быть WinAVR или тулчейн AVR-GCC, который устанавливается в составе Atmel Studio).

[4. Обработка передачи USART]

Обработка передачи будет простейшая: в главный цикл main будет вставлена процедура handlerTXUSART, проверяющая наличие данных в буфере передачи. Если данные в буфере передачи есть, и передатчик свободен, то из буфера передачи будет выбран байт и записан в регистр UDR0.

Минимальная настройка завершена. Все, что будет попадать в буфер передачи bufTX, будет выведено через USART0. Все, что поступит из внешнего мира, попадет в буфер приема bufRX. Само собой основной код должен использовать эту возможность, чтобы осуществлять обмен данными через USART, т. е. при необходимости нужно читать буфер приема и писать данные в буфер передачи. Все остальное будет происходить автоматически.

Что можно улучшить: если написать обработчик прерывания опустошения буфера передатчика, то можно ускорить передачу. В этом обработчике можно делать то же самое, что осуществляется в подпрограмме handlerTXUSART, за исключением того, что не нужно проверять флаг UDRE0, достаточно проверить только наличие данных в кольцевом буфере bufTX.

[5. Настройка printf на вывод через USART]

Перенаправление printf в USART нужно в основном чисто для удобства: чтобы проще выводить нужные отладочные (или какие-то другие) текстовые сообщения в какое-то устройство, где их можно отобразить и прочитать. Если для перенаправления используется USART (можно кстати использовать и другие устройства вывода текста, например экран LCD), то выводимые текстовые сообщения можно увидеть на компьютере в окне программы-терминала (например, putty, TerraTerm, HyperTerminal, Serial Monitor у Arduino IDE), подключенной к COM-порту, куда поступают данные от микроконтроллера (обычно это виртуальный COM-порт через соединение USB, как например это сделано у плат Arduino). Короче говоря, задача состоит в том, чтобы текст, который выводится оператором printf, сразу попадал в консоль программы терминала.

Описание решения этой задачи подробно описано в [4], здесь я просто кратко покажу что нужно сделать. Вывод в USART через printf с использованием библиотек avr-libc настраивается за 3 простых шага (последний шаг необязательный):

1. Подключить заголовочный файл stdio.h.

2. Определить функцию, которая будет выводить символ в UART (в этом примере функция uart_putchar).

3. (Необязательно) опциями линкера выбрать вариант обработки преобразований формата printf.

Здесь настраивается поток mystdout, который привязывается к функции вывода символа и стандартному потоку вывода stdout.

Если пропустить шаг 3, то оператор printf будет работать с ограничениями при обработке формата для чисел с плавающей запятой (подробнее про это и про опции настройки линкера см. [4]).

Как уже упоминалось, у ATmega2560 имеется 4 последовательных порта USART: USART0, USART1, USART2 и USART3, которые фиксировано привязаны к определенным ножкам корпуса микроконтроллера. Т. е. определенный вывод микроконтроллера может работать либо просто как порт ввода/вывода, либо как аппаратный вход или выход интерфейса USART. Все зависит от программной настройки — данных, которые Вы запишете в управляющие регистры микроконтроллера. В таблице и на картинке показана привязка аппаратуры USART к выводам микроконтроллера.

| Имя | Прерывания | Регистры | Порты RXD, TXD, XCK |

| USART0 | UDRE0, TXC0, RXC0 | UDR0, UCSR0A, UCSR0B, UCSR0C, UBRR0L, UBRR0H | PE0, PE1, PE2 |

| USART1 | UDRE1, TXC1, RXC1 | UDR1, UCSR1A, UCSR1B, UCSR1C, UBRR1L, UBRR1H | PD2, PD3, PD5 |

| USART2 | UDRE2, TXC2, RXC2 | UDR2, UCSR2A, UCSR2B, UCSR2C, UBRR2L, UBRR2H | PH0, PH1, PH2 |

| USART3 | UDRE3, TXC3, RXC3 | UDR3, UCSR3A, UCSR3B, UCSR3C, UBRR3L, UBRR3H | PJ0, PJ1, PJ2 |

Порты USART обладают следующими основными возможностями:

• Поддерживают полный дуплекс (имеют независимые аппаратные буферы приема и передачи).

• Могут работать асинхронно и синхронно.

• В синхронном режиме могут либо вырабатывать такты, либо использовать внешнее тактирование (Master or Slave Clocked Synchronous Operation).

• Генератор скорости передачи, настраиваемый с высокой точностью (High Resolution Baud Rate Generator).

• Поддерживает размеры фрейма передачи из 5, 6, 7, 8 или 9 бит данных и 1 или 2 стоповых бита.

• Аппаратная поддержка генерации и проверки на нечетность или четность (Odd or Even Parity).

• Детектирование потери данных на приеме (Data OverRun Detection).

• Детектирование ошибок фрейма (Framing Error Detection).

• Фильтрация помех (Noise Filtering) с помощью цифрового ФНЧ, включающая детектирования ошибочного стартового бита.

• 3 отдельных прерывания по событиям TX Complete, TX Data Register Empty и RX Complete.

• Режим обмена с несколькими процессорами (Multi-processor Communication Mode).

• Асинхронный режим с двойной скоростью (Double Speed Asynchronous Communication Mode).

Для уменьшения общего энергопотребления кристалла ненужные USARTn могут быть полностью выключены с помощью битов управления регистров PRR0 и PRR1.

Порт USART0 используется в платах Arduino Mega 2560 [2] под аппаратный мост USB-UART, чтобы обеспечить работу загрузчика кода и поддержку отладочного вывода через Serial Monitor.

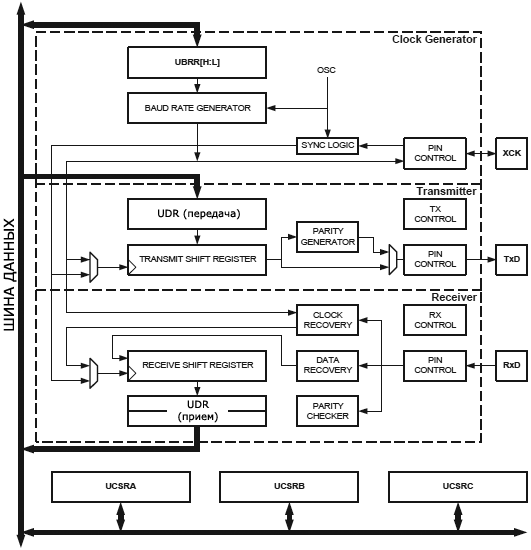

Рис. 22-1. Блок-диаграмма внутреннего устройства USART.

На диаграмме пунктирными линиями выделены 3 отдельных блока USART (перечисленные далее сверху вниз): Clock Generator (тактовый генератор), Transmitter (передатчик) и Receiver (приемник). Регистры управления общие для всех этих блоков. Логика Clock Generation состоит из логики синхронизации для внешних тактов (SYNC LOGIC, используется в подчиненном режиме для синхронизации передачи бит), и генератора скорости передачи (BAUD RATE GENERATOR). Вывод XCKn (такты передачи) используется только для синхронного режима работы (synchronous transfer mode). Передатчик состоит из одиночного буфера записи (UDR), последовательного регистра сдвига (TRANSMIT SHIFT REGISTER), генератора четности (PARITY GENERATOR) и логики управления (TX CONTROL) для поддержки разных форматов фрейма. Наличие аппаратного буфера фрейма позволяет вести непрерывные передачи без задержек между отдельными фреймами. Приемник наиболее сложный узел USART, потому что он имеет узлы восстановления тактов (CLOCK RECOVERY) и данных (DATA RECOVERY), которые используются для асинхронного приема данных. В дополнение к узлам восстановления приемник содержит блок проверки на четность (PARITY CHECKER), логику управления (RX CONTROL), регистр сдвига и двухуровневый буфер приема (UDR). Приемник поддерживает одинаковый формат фрейма, который использует передатчик, и может детектировать ошибку фрейма (Frame Error), событие потери данных на приеме (Data OverRun) и ошибку четности (Parity Error). Модуль PIN CONTROL управляет поведением порта микроконтроллера — или этот вывод работает как обычный порт ввода/вывода GPIO, или он подключен к аппаратуре USART и выполняет специальную функцию.

[Генерация тактов]

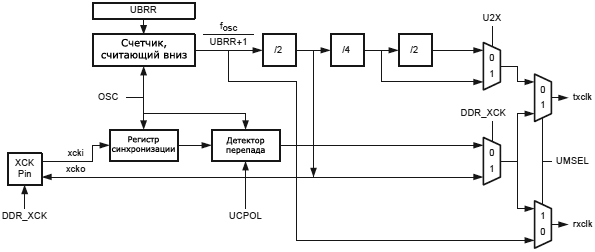

Логика генерации тактов синтезирует базовую частоту синхронизации для передатчика и приемника. The USARTn поддерживает 4 режима тактирования: нормальный асинхронный (Normal asynchronous), асинхронный двойной скорости (Double Speed asynchronous), синхронный главный (Master synchronous) и синхронный подчиненный (Slave synchronous). Бит UMSELn в USART Control and Status Register C (UCSRnC) выбирает между асинхронным и синхронным режимами. Двойная скорость (применимо только к асинхронному режиму) управляется битом U2Xn, находящемся в регистре UCSRnA. Когда используется синхронный режим (UMSELn = 1), регистр направления данных (Data Direction Register, DDR) для вывода XCKn определяет, каким будет тактирование для синхронного режима: внутренним (Master mode) или внешним (Slave mode). Вывод XCKn активен только в при использовании синхронного режима, в асинхронном режиме он работает как простой порт GPIO.

Рис. 22-2. Блок-диаграмма логики генерации тактов USART.

txclk такты передатчика (внутренний сигнал).

rxclk базовые такты передатчика (внутренний сигнал).

xcki ввод от вывода XCK (внутренний сигнал). Используется для работы в синхронном подчиненном режиме (synchronous slave operation).

xcko выходной сигнал тактов для подачи на вывод XCK (внутренний сигнал). Используется для работы в синхронном подчиненном режиме (synchronous master operation).

fOSC частота вывода XTAL (System Clock, системная частота).

DDR_XCK разряд регистра DDRX, управляющий направлением работы ножки порта (вход или выход).

Baud Rate Generator, внутренняя генерация тактов. Генерация тактов внутри чипа используется для асинхронного и синхронного режимов работы. USART Baud Rate Register (UBRRn) и считающий вниз счетчик (Prescaling Down-Counter) подключены к программируемому прескалеру, или другими словами к генератору скорости передачи (Baud Rate Generator). Обратно-считающий счетчик (down-counter), работающей на системной частоте (fOSC), каждый раз загружается значением из UBRRn, когда счетчик достигает нуля, или когда записан регистр UBRRLn. В этот момент генерируется тактовый импульс для USART, появляющийся на выходе Baud Rate Generator (= fOSC/(UBRRn+1)). Передатчик делит выходную тактовую частоты Baud Rate Generator на 2, 8 или 16 в зависимости от режима. Выход Baud Rate Generator напрямую используется для тактирования приемника и узлов восстановления данных. Однако узлы восстановления используют машину состояний из 2, 8 или 16 состояний в зависимости от режима, установленного битами UMSELn, U2Xn и DDR_XCKn.

Таблица 22-1 содержит выражения для вычисления скорости baud rate (в битах на секунду) и для вычисления значения UBRRn для каждого режима работы, когда используется генерируемый внутри источник тактов.

Табл. 22-1. Формулы для расчета скорости и настроек в зависимости от режима.

| Режим | Скорость (1) | UBRR |

| Асинхронный нормальный (U2XN = 0) | fOSC BAUD = ———————— 16 * (UBRRn+1) |

fOSC UBRRn = —————- — 1 16 * BAUD |

| Асинхронный двойной скорости (U2XN = 1) | fOSC BAUD = ———————— 8 * (UBRRn+1) |

fOSC UBRRn = ————— — 1 8 * BAUD |

| Синхронный главный | fOSC BAUD = ———————— 2 * (UBRRn+1) |

fOSC UBRRn = ————— — 1 2 * BAUD |

Примечание (1). Скорость передачи определена как скорость следования бит в секунду (baud rate, bit per second, bps).

BAUD Baud rate (в битах/сек, bps).

fOSC системная тактовая частота (System Oscillator clock frequency).

UBRRn содержимое регистров UBRRHn и UBRRLn (0-4095).

Некоторые примеры значений UBRRn для разных тактовых частот микроконтроллера можно найти в таблице 22-9.

Double Speed Operation (U2Xn). Скорость передачи может быть удвоена (это пошло еще от микроконтроллеров серии MCS51) путем установки бита U2Xn в регистре UCSRnA. Установка этого бита дает эффект только для асинхронной работы USART, сбросьте этот бит в 0 для синхронного функционирования.

Установка бита U2Xn уменьшит коэффициент деления синтезатора скорости с 16 до 8, что соответствует удвоению скорости передачи и приема для асинхронного режима. Имейте в виду, что приемник в этом случае будет делать в 2 раза меньше выборок при восстановлении данных и тактов (количество выборок также уменьшиться с 16 до 8), так что для удвоения скорости с сохранением точной установки скорости понадобится более точно выдерживать системную частоту. Это важно для приемника, а для передатчика нет никаких проблем.

Внешнее тактирование. Используются в подчиненном синхронном режиме работы. Внешние такты поступают от вывода XCKn (см. рис. 22-2), и их значения выбираются регистром синхронизации, чтобы уменьшить шансы нестабильности. Выход регистра синхронизации затем должен поступить сначала на детектор перепада, перед тем как сигнал тактов можно было использовать в передатчике и приемнике. Этот процесс занимает два цикла системной тактовой частоты CPU, так что эта задержка ограничивает максимально возможную тактовую частоту XCKn:

fOSC

fXCK Примечание: эти функции передачи написаны только для примера. Они могут быть оптимизированы, если содержимое UCSRnB статическое. Например, после инициализации в регистре UCSRnB используется только бит TXB8.

9-й бит может использоваться для того, чтобы показать адрес фрейма в режиме обмена с несколькими процессорами (multi processor communication mode) или для другого протокола, например для синхронизации.

Флаги передатчика и прерывания. У передатчика USART есть 2 флага, которые показывают его состояние: USART Data Register Empty (UDREn) и Transmit Complete (TXCn). Оба флага можно использовать для генерации прерываний.

Флаг Data Register Empty (UDREn) показывает, готов или нет буфер передачи к записи туда новых данных. Этот бит устанавливается, когда буфер передачи опустошается, и очищается, когда буфер передачи содержит данные для отправки, которые еще пока не перемещены в регистр сдвига. Для совместимости с микроконтроллерами, которые возможно появятся в будущем, всегда записывайте этот бит в 0, когда записываете регистр UCSRnA.

Когда в бит Data Register Empty Interrupt Enable (UDRIEn) регистра UCSRnB записана 1, будет возможен запуск прерывания USART Data Register Empty, если установлен бит UDREn (подразумевается, что глобально прерывания разрешены).

UDREn очищается путем записи UDRn. Когда используется передача данных с управлением по прерываниям, подпрограмма прерывания Data Register Empty должна либо записать новые данные в UDRn, чтобы очистить UDREn, либо запретить прерывание Data Register Empty, иначе новое прерывание запустится после завершения обработчика прерывания.

Бит флага Transmit Complete (TXCn) устанавливается в 1, когда весь фрейм в регистре сдвига передачи будет выдвинут наружу, и в буфере передачи нет новых данных. Бит флага TXCn Flag автоматически очищается, когда запускается прерывание transmit complete, или этот флаг может быть очищен записью в него лог. 1. Флаг TXCn полезен при полудуплексном обмене (наподобие стандарта RS-485), где передающее приложение должно войти в режим приема и немедленно освободить шину обмена после завершения передачи.

Если бит Transmit Compete Interrupt Enable (TXCIEn) в регистре UCSRnB установлен, запустится прерывание USART Transmit Complete, когда установится флаг TXCn (подразумевается, что глобально прерывания разрешены). Когда используется прерывание transmit complete, обработчику прерывания не нужно очищать флаг TXCn, это автоматически произойдет, когда сработает прерывание.

Parity Generator. Генератор четности (Parity Generator) вычисляет бит четности для последовательного фрейма данных. Когда разрешен бит четности (UPMn1 = 1), логика управления передатчиком вставляет бит четности между последним битом данных и первым stop-битом отправляемого фрейма.

Запрет передатчика. Запрет передатчика (сброс TXEN в 0) не вступит в силу, пока происходит активная передача, т. е. пока регистр сдвига и регистр буфера передачи еще содержат данные для передачи. После того, как передатчик запрещен, но больше не будет переназначать вывод порта TxDn.

[Прием данных – USART Receiver]

Приемник USART разрешатся путем записи бита Receive Enable (RXENn) регистра UCSRnB в 1. Когда приемник разрешен, нормальная работа порта RxDn переназначается аппаратурой USART, и этот порт становится входом приемника для последовательных данных. Параметры baud rate, режима работы и формат фрейма должны быть установлены до того, как можно будет осуществлять любой прием. Если используется синхронный режим, то вывод XCKn будет использоваться как такты приема.

Прием фреймов длиной от 5 до 8 бит данных. Приемник начнет прием данных, когда детектирует допустимый start-бит. Каждый бит, который следует за стартовым, будет оцифровывается на скорости baud rate, или с тактами XCKn, и вдвигаться регистр сдвига, пока не будет принят первый stop-бит фрейма. Второй stop-бит будет приемником игнорироваться. Когда будет принят первый stop-бит, т. е. когда полный фрейм присутствует в регистре сдвига, то содержимое регистра сдвига будет перемещено в буфер приема. Буфер приема может быть прочитан через UDRn.

Следующий пример кода показывает простую функцию приема USART на базе опроса флага Receive Complete (RXCn). Когда используются фреймы размером меньше 8 бит, самый старший бит байта данных, прочитанного из UDRn, будет маскирован нулем. USART должен быть инициализирован перед использованием этой функции.

Функция просто ждет появления данных в буфере приема путем проверки флага RXCn перед чтением буфера и возврата значения. Это означает, что она полностью блокирует программу, если на вход USART не поступают данные.

Прием фреймов длиной 9 бит данных. Если используются 9-битные символы (UCSZn=7), то 9-й бит должен быть прочитан из бита RXB8n регистра UCSRnB до чтения младших 8 бит из UDRn. То же самое правило действует и для флагов состояния FEn, DORn и UPEn. Сначала прочитайте состояние из UCSRnA, затем данные из UDRn. Чтение UDRn по его адресу I/O поменяет состояние приемного буфера FIFO и следовательно поменяется состояние битов TXB8n, FEn, DORn и UPEn, которые все сохраняются в FIFO.

Следующий пример кода покажет простую функцию приема USART, которая обрабатывает как 9-й бит, так и биты статуса.

Пример функции приема читает все регистры I/O в регистровый файл перед тем, как вычисления завершаться. Это дает оптимальное использование буфера, поскольку чтение ячеек буфера нужно выполнить как можно быстрее, чтобы освободить их с целью получения новых данных.

Флаг и прерывание Receive Compete. У приемника USART есть 1 флаг, который показывает состояние приемника. Флаг Receive Complete (RXCn) показывает, что в буфере приема есть не прочитанные данные. Этот флаг равен 1, когда не прочитанные данные есть в буфере приема, и 0, когда буфер приема пуст (т. е. в нем не содержится никаких не прочитанных данных). Если приемник запрещен (RXENn = 0), буфер приема сбрасывается, и следовательно флаг RXCn обнуляется.

Когда установлен бит Receive Complete Interrupt Enable (RXCIEn) в регистре UCSRnB, выполнится прерывание USART Receive Complete, когда флаг RXCn установится (подразумевается, что глобально прерывания разрешены). Когда работает прием данных по прерываниям, то подпрограмма обработчика прерывания Receive Complete должна прочитать принятые данные UDRn, чтобы очистить флаг RXCn, иначе после завершения работы обработчика прерывания снова запуститься тот же обработчик прерывания.

Флаги ошибок приемника. У приемника USART есть 3 флага ошибки: Frame Error (FEn), Data OverRun (DORn) и Parity Error (UPEn). Все биты ошибок доступны через чтение UCSRnA. Общим для флагов ошибок является то, тчо они размещены в буфере приема вместе с данными фрейма, для которого флаги ошибок показывают состояние (т. е. буферизация данных фрейма привязана к буферизации флагов ошибки). По этой причине сначала нужно прочитать UCSRnA, и только потом буфер данных приема (UDRn), поскольку чтение UDRn по его месту размещения I/O освободит буфер под новые данные. Еще флаги ошибок объединяет то, что их нельзя сбросить программно записью. Однако для обеспечения совместимости с изменениями в USART, которые возможно появятся в будущем, все флаги должны быть сброшены в 0, когда осуществляется запись UCSRnA. Флаги ошибки не могут генерировать прерывание.

Флаг Frame Error (FEn) показывает состояние первого stop-бита принятого фрейма, находящегося в буфере приема. Флаг FEn равен 0, если stop-бит был прочитан правильно (как 1), и флаг FEn будет в 1, когда stop-бит ошибочен (равен 0). Этот флаг может использоваться для детектирования событий выхода из синхронизации, событий остановки потока (break conditions) и поддержки обработки протокола. На флаг FEn не влияет настройка бита USBSn в регистре UCSRnC, поскольку приемник игнорирует все stop-биты, кроме первого. Для обеспечения совместимости с микроконтроллерами, который возможно появятся в будущем, всегда сбрасывайте этот бит в 0, когда записываете UCSRnA.

Флаг Data OverRun (DORn) показывает потерю данных, из-за того, что у буфере приемника были не прочитанные данные. Data OverRun произойдет, когда буфер приема заполнен (в нем находится 2 символа), ожидается прием следующего символа, и детектирован новый start-бит. Если флаг DORn установлен, то была потеря одного или большего количества фреймов между последним чтением и следующим чтением фрейма из UDRn. Для обеспечения совместимости с микроконтроллерами, который возможно появятся в будущем, всегда записывайте этот бит в 0, когда записываете UCSRnA. Флаг DORn очищается, когда принятый фрейм успешно перемещен из регистра сдвига в буфер приема.

Флаг ошибки четности Parity Error (UPEn) показывает, что следующий фрейм, находящийся в буфере приема, имеет ошибку четности на приеме. Если контроль четности не разрешен, то бит UPEn будет всегда читаться как 0. Для обеспечения совместимости с микроконтроллерами, который возможно появятся в будущем, всегда сбрасывайте этот бит в 0, когда пишете в UCSRnA.

Узел проверки бита четности (Parity Checker) активен, когда установлен в 1 бит USART Parity mode (UPMn1). Тип выполняемой проверки на четность (нечетность odd или четность even) выбирается битом UPMn0. Когда проверка четности разрешена, Parity Checker вычисляет четность от бит данных приходящих фреймов, и сравнивает результат с битом четности из последовательного фрейма. Результат проверки сохраняется в буфере приема вместе с принятыми данными и stop-битами. Флаг Parity Error (UPEn) может быть прочитан программно, чтобы проверить, была ли во фрейме ошибка четности.

Бит UPEn установится, если в следующем символе, который можно прочитать из буфера приема, была ошибка четности на приеме, и проверка четности в этот момент была разрешена (UPMn1 = 1). Этот бит действителен, пока не произойдет чтение буфера приема (регистра UDRn).

Запрет приемника. В отличие от передатчика, запрет приемника срабатывает немедленно. Таким образом, принимаемый в настоящий момент фрейм данных (и конечно последующие после запрета) будут потеряны. Когда приемник запрещен (т. е. RXENn сброшен в 0), то он больше не переназначает нормальную работу порта RxDn как ножки GPIO. При запрете приемника буфер FIFO приемника будет сброшен, все оставшиеся в нем непрочитанные данные будут потеряны.

Сброс буфера приема. Буфер FIFO приемника будет сброшен, когда приемник запрещен, т. е. запомненные в буфере данные уничтожаются, непрочитанные данные будут потеряны. Если нужно сбросить буфер во время нормальной работы, например по причине события ошибки, просто делайте чтение UDRn, пока флаг RXCn не очистится. В следующем примере кода показана очистка буфера приема.

[Асинхронный прием данных]

В состав USART включены блоки восстановления тактов (Asynchronous Clock Recovery) и данных (Asynchronous Data Recovery), чтобы поддержать асинхронный прием данных. Логика восстановления используется для синхронизации генерируемых внутри тактов скорости (baud rate) для входящих асинхронных последовательных фреймов на выводе RxDn. Логика восстановления данных оцифровывает и пропускает через ФНЧ каждый бит приходящих данных, чтобы улучшить стойкость приемника к помехам. Диапазон работоспособности асинхронного приема зависит от точности внутренних тактов скорости, скорости входящих фреймов, размера фрейма в количестве бит.

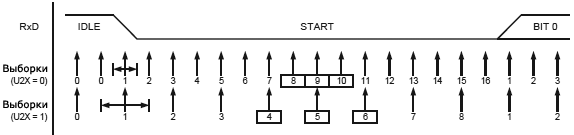

Asynchronous Clock Recovery. Логика восстановления тактов синхронизирует внутренние такты по входящим последовательным фреймам. На рис. 22-5 показан процесс оцифровки стартового бита входящего фрейма. Частота оцифровки в 16 раз больше частоты бит (baud rate) для нормального режима (Normal mode), и в 8 раз больше частоты бит для режима двойной скорости (Double Speed mode). Горизонтальные стрелки показывают интервалы подстройки синхронизации в процессе оцифровки. Обратите внимание на увеличенные интервалы для режима двойной скорости (Double Speed mode, U2Xn = 1). Выборки, помеченные нулями, означают выборки, когда сигнал RxDn в состоянии ожидания idle (т. е. нет активной передачи).

Рис. 22-5. Выборка (оцифровка) start-бита.

Когда логика восстановления тактов детектировала переход от лог. 1 (idle) к лог. 0 (start) на линии RxDn, инициируется последовательность детектирования start-бита. Выборка 1 на рисунке показывает первую нулевую выборку. Затем логика восстановления тактов использует выборки 8, 9 и 10 для нормального режима, и выборки 4, 5 и 6 для режима двойной скорости (эти цифры выделены прямоугольной рамкой на рисунке), чтобы определить, что действительно принят допустимый start-бит. Если 2 или большее количество этих выборок имеют лог. 1 (принцип большинства), то start-бит отбрасывается как шумовая помеха, и приемник снова начинает детектирование следующего перехода от 1 к 0. Однако если детектирован допустимый start-бит («большинство» указывает на 0), то в логика восстановления тактов синхронизируется, и может начаться процесс восстановления данных. Процесс синхронизации повторяется для каждого start-бита.

Asynchronous Data Recovery. Когда произошла синхронизация тактов приемника по start-биту, может начать работу восстановление данных. Блок восстановления данных использует машину из 16 состояний для каждого бита в нормальном режиме и машину 8 состояний для режима двойной скорости. На рис. 22-6 показана оцифровка битов данных и бита четности (BITn). Каждая выборка помечена цифрой, которая равна состоянию блока восстановления.

Рис. 22-6. Выборка данных и бита четности.

Принятие решения о лог. уровне принятого бита выполняется по тому же самому «принципу большинства» на 3 выборках посередине принимаемого бита. Номера этих выборок помечены на рисунке рамочками. Если 2 или большее количество из этих 3 выборок прочитаны как 1, то принятый бит регистрируется как лог. 1. И аналогично если 2 или большее количество из этих 3 выборок прочитаны как 0, то принятый бит регистрируется как лог. 0. Этот принцип работает как простейший цифровой ФНЧ для входящего сигнала на выводе RxDn. Процесс восстановления данных повторяется для каждого бита, пока не завершится прием всего фрейма, включая первый stop-бит. Имейте в виду, что приемник использует только первый stop-бит фрейма.

На рис. 22-7 показана оцифровка stop-бита как можно раньше относительно начала start-бита следующего фрейма.

Рис. 22-7. Выборка стоп-бита и следующего стартового бита.

Для оцифровки (получения значения) stop-бита применяется тот же самый мажоритарный принцип голосования, как и для других бит фрейма. Если определено, что stop-бит равен лог. 0, то регистрируется ошибка фрейма, и будет установлен флаг Frame Error (FEn).

Новый переход 1 -> 0 покажет начало start-бита нового фрейма, и он может появиться сразу после последнего бита, в котором использовалось детектирование уровня по мажоритарному принципу. Для режима Normal Speed, первая выборка с низким уровнем может быть в точке, промаркированной как (A) на рис. 22-7. Для Double Speed mode первый низкий уровень должен быть задержан до (B). (C) помечает stop-бит полной длины. Раннее детектирование start-бита влияет на рабочий диапазон приемника (Asynchronous Operational Range).

Asynchronous Operational Range. Рабочий диапазон приемника зависит от несоответствия скорости принимаемых бит и генерируемой внутри скорости. И передатчик, и приемник должны быть настроены на одну и ту же скорость, но из-за погрешности частоты системного тактового генератора реальные частоты могут отличаться. Если передатчик посылает фреймы со слишком большой частотой бит или слишком малой частотой бит, или если генерируемая частота бит приемника имеет отличающуюся базовую частоту (см. таблицу 22-2), то приемник не сможет синхронизировать фреймы по start-биту.

Следующие формулы можно использовать для вычисления соотношения между скоростью принимаемых данных и внутренней скоростью приемника.

| (D + 1) * S Rslow = ———————- S — 1 + D*S + SF |

(D + 2) * S Rfast = ———————- (D + 1) * S + SM |

D сумма числа бит символа и бита четности (D = 5 .. 10 бит).

S количество выборок на бит, S = 16 для Normal Speed mode и S = 8 для Double Speed mode.

SF номер первой выборки, используемой для детектирования уровня по мажоритарному принципу. SF = 8 для Normal Speed mode и SF = 4 для Double Speed mode.

SM номер средней выборки, используемой для детектирования уровня по мажоритарному принципу. SM = 9 для Normal Speed mode и SM = 5 для Double Speed mode.

Rslow соотношение между самой низкой входной скоростью и собственной скоростью приемника, при котором приемник все еще может принимать данные.

Rfast соотношение между самой высокой входной скоростью и собственной скоростью приемника, при котором приемник все еще может принимать данные.

Таблицы 22-2 и 22-3 дают список максимально допустимой ошибки baud rate приемника. Обратите внимание, что для Normal Speed mode допуск больше.

Табл. 22-2. Рекомендуемые максимальные скорости передачи и погрешность приемника для нормального режима скорости (U2Xn = 0).

| D (Data + Parity Bit) | Rslow (%) | Rfast (%) | MAX общая ошибка, % | Рекомендуемая MAX ошибка приемника, % |

| 5 | 93.20 | 106.67 | +6.67 / -6.8 | ±3.0 |

| 6 | 94.12 | 105.79 | +5.79 / -5.88 | ±2.5 |

| 7 | 94.81 | 105.11 | +5.11 / -5.19 | ±2.0 |

| 8 | 95.36 | 104.58 | +4.58 / -4.54 | ±2.0 |

| 9 | 95.81 | 104.14 | +4.14 / -4.19 | ±1.5 |

| 10 | 96.17 | 103.78 | +3.78 / -3.83 | ±1.5 |

Табл. 22-3. Рекомендуемые максимальные скорости передачи и погрешность приемника для двойной скорости (U2Xn = 1).

| D (Data + Parity Bit) | Rslow (%) | Rfast (%) | MAX общая ошибка, % | Рекомендуемая MAX ошибка приемника, % |

| 5 | 94.12 | 105.66 | +5.66 / -5.88 | ±2.5 |

| 6 | 94.92 | 104.92 | +4.92 / -5.08 | ±2.0 |

| 7 | 95.52 | 104.35 | +4.35 / -4.48 | ±1.5 |

| 8 | 96.00 | 103.90 | +3.90 / -4.00 | ±1.5 |

| 9 | 96.39 | 103.53 | +3.53 / -3.61 | ±1.5 |

| 10 | 96.70 | 103.23 | +3.23 / -3.30 | ±1.0 |

Рекомендации по максимальной ошибке baud rate приемника были сделаны на основе предположения, что и приемник, и передатчик разделяют одинаковую максимальную погрешность частоты.

Есть 2 возможных источника ошибок baud rate приемника. Системная тактовая частота приемника (XTAL) всегда будет незначительно зависеть от напряжения питания и температуры окружающей среды. Когда для генерации системной частоты используется кварц, то в этом случае проблем чаще всего не будет. Однако если применить некачественный резонатор с допуском более 2%, то это может послужить причиной ошибок. Второй источник ошибки более управляемый. Генератор baud rate не всегда делает точное деление системной частоты, чтобы получить желаемое значение baud rate. В этом случае желательно использовать то значение для UBRR, которое дает ошибку как можно меньше.

[Multi-processor Communication Mode]

Установка бита Multi-processor Communication mode (MPCMn) в регистре UCSRnA разрешает функцию фильтрации входящих фреймов, полученных приемником USART. Фреймы, которые не содержат информацию адреса, будут игнорироваться и не попадут в буфер приема. Это эффективно уменьшит количество входящих фреймов, которые должны быть программно обработаны CPU в системе, где несколько процессоров (MCU) обмениваются данными по одной и той же последовательной шине данных. На передатчик не влияет установка бита MPCMn, но передатчик должен использоваться по-другому, когда он работает как часть системы, использующей Multi-processor Communication mode.

Если приемник настроен для приема фреймов, содержащих от 5 до 8 бит данных, то первый stop-бит показывает, есть ли во фрейме информация адреса. Если приемник настроен на фреймы с 9 битами данных, то 9-й бит (RXB8n) используется для идентификации фреймов адреса и данных. Когда бит типа фрейма (это первый stop-бит или 9-й бит) равен 1, то фрейм содержит адрес. Когда бит типа фрейма равен 0, то это будет фрейм данных.

Multi-processor Communication mode разрешает нескольким подчиненным MCU принимать данные от главного MCU. Это осуществляется путем декодирования фрейма адреса, чтобы определить, какой именно MCU адресован на шине. Если адресован конкретный подчиненный MCU, то он примет следующие фреймы данных как обычно, в то время другие подчиненные MCUs будут игнорировать принятые фреймы, пока не будет принят другой адресный фрейм.

Использование MPCMn. Для MCU, который работает как главный на общей шине, можно использовать 9-битный формат фрейма (UCSZn = 7). Девятый бит (TXB8n) должен быть установлен, когда передается фрейм адреса (TXB8n = 1), или очищен, когда передается фрейм данных (TXB = 0). Подчиненные MCU в этом случае должны быть настроены для использования 9-битного формата фрейма.

Для обмена данными в Multi-processor Communication mode должна использоваться следующая процедура:

1. Все подчиненные MCU настроены в Multi-processor Communication mode (установлен бит MPCMn в регистре UCSRnA).

2. Главный MCU посылает фрейм адреса, и все подчиненные устройства принимают и читают этот фрейм. В подчиненных MCU флаг RXCn в регистре UCSRnA будет установлен как обычно.

3. Каждый подчиненный MCU читает регистр UDRn, чтобы определить, что для приема выбран именно он (проверяет совпадение адреса). Если так, то он очищает бит MPCMn в регистре UCSRnA, в противном случае просто ждет следующего адресного фрейма, сохраняя установленным бит MPCMn.

4. Адресованный MCU будет принимать все фреймы данных, пока не поступит новый фрейм адреса. Другие подчиненные MCUs, у которых установлен бит MPCMn, будут (аппаратно) игнорировать фреймы данных.

5. Когда адресованный MCU примет последний фрейм данных, то он устанавливает бит MPCMn и ждет новый фрейм адреса от главного MCU. Затем процедура повторяется начиная с шага 2.

Можно использовать любой формат фрейма от 5 до 8 бит, но это непрактично, потому что приемник нужно перепрограммировать между использованием n и n+1 форматом бит фрейма. Это делает полнодуплексный обмен сложным, потому что передатчик и приемник используют настройку для одного и того же размера символа. Если используется формат символа от 5 до 8 бит, то передатчик должен быть установлен на использование двух stop-битов (USBSn = 1), поскольку первый stop-бит используется для указания типа фрейма (адрес или данные).

Не используйте инструкции ассемблера Read-Modify-Write (SBI и CBI) для установки или очистки бита MPCMn. Бит MPCMn использует то же самое место в пространстве I/O, как и флаг TXCn, и это может случайно очистить его при использовании инструкций SBI или CBI.

USART ATmega2560 может также работать в режиме SPI, но здесь этот вариант настройки USART не рассматривается.

UDRn – USART I/O Data Register n

| № разрядов | 7 | 6 | 5 | 4 | 3 | 2 | 1 | |

| Регистры |

RXB[7:0] (UDRn при чтении) |

|||||||

| TXB[7:0] (UDRn при записи) | ||||||||

| Чтение/запись | rw | rw | rw | rw | rw | rw | rw | rw |

| Нач. значение |

Регистры USART Transmit Data Buffer (TXB) и Receive Data Buffer (RXB) разделяют одну и ту же ячейку пространства адресов I/O, которая носит мнемоническое название USART Data Register, или UDRn. TXB будет точкой назначения для записываемых в UDRn данных. Чтение UDRn вернет данные из RXB.

Для 5, 6 или 7-разрядных символов верхние неиспользуемые биты будут игнорироваться при передаче и автоматически обнуляться при приеме.

Буфер передачи можно записать только тогда, когда установлен флаг UDREn в регистре UCSRnA. Данные, записанные в UDRn, когда флаг UDREn не установлен, будут игнорироваться передатчиком USART. Если данные записаны в буфер передачи, и передатчик разрешен, то передатчик загрузит данные в регистр сдвига передачи, когда регистр сдвига пуст. Тогда данные будут последовательно передаваться через вывод TxDn.

Буфер приема состоит из 2-уровневого FIFO. FIFO поменяет свое состояние независимо от того, был ли к нему доступ, или нет. Из-за этого поведения буфера приема не используйте для него инструкции ассемблера Read-Modify-Write (SBI и CBI). Будьте осторожны, когда используете инструкции проверки бит (SBIC и SBIS), поскольку они также изменят состояние FIFO.

UCSRnA – USART Control and Status Register A

| № разрядов | 7 | 6 | 5 | 4 | 3 | 2 | 1 | |

| Имена бит | RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn |

| Чтение/запись | r | rw | r | r | r | r | rw | rw |

| Нач. значение | 1 |

• 7 – RXCn: USART Receive Complete

Этот флаг установится, когда в буфере приема есть непрочитанные данные, и очищается, когда буфер приема пуст (т. е. в нем не содержатся какие-либо непрочитанные данные). Если приемник запрещен, то буфер приема сбрасывается, следовательно бит RXCn становится нулем. Флаг RXCn может использоваться для генерации прерывания Receive Complete (см. описание бита RXCIEn).

• 6 – TXCn: USART Transmit Complete

Этот бит установится, когда весь фрейм в регистре сдвига передачи выдвинут на выход, так что в настоящий момент нет новых данных в буфере передачи (UDRn). Флаг TXCn автоматически очищается, когда запускается прерывание Transmit Complete, или этот бит может быть очищен программно записью туда 1. Флаг TXCn может генерировать прерывание Transmit Complete (см. описание бита TXCIEn).

• 5 – UDREn: USART Data Register Empty

Флаг UDREn показывает, что буфер передачи (UDRn) пуст и готов к записи туда новых данных. Если бит UDREn в состоянии 1, то буфер пуст, и туда можно записать новый символ для передачи. Флаг UDREn может генерировать прерывание Data Register Empty (см. описание бита UDRIEn).

UDREn устанавливается после сброса, показывая этим, что передатчик готов к работе.

• 4 – FEn: Frame Error

Этот бит установится, если следующий символ в буфере приема получил ошибку фрейма, т. е. когда первый stop-бит оказался нулевым. Этот бит действителен, пока не будет прочитан буфер приема (UDRn), т. е. этот флаг привязан с принятому символу. FEn равен 0, когда stop-бит принятого фрейма равен 1 (нормальная ситуация, ошибки нет). Всегда сбрасывайте этот бит, когда записываете регистр UCSRnA.

• 3 – DORn: Data OverRun

Этот бит установится, если детектировано событие Data OverRun. Оно произойдет, когда буфер приема заполнен (в нем находится 2 принятых символа), ожидается прием нового символа, и был детектирован новый start-бит. Этот бит действителен, пока не будет прочитан буфер приема (UDRn), т. е. этот флаг привязан с принятому символу. Всегда сбрасывайте этот бит, когда записываете регистр UCSRnA.

• 2 – UPEn: USART Parity Error

Этот бит установится, если следующий символ в буфере приема имеет ошибку четности на приеме, и в момент его приема была разрешена проверка четности (UPMn1 = 1). Этот бит действителен, пока не будет прочитан буфер приема (UDRn), т. е. этот флаг привязан с принятому символу. Всегда сбрасывайте этот бит, когда записываете регистр UCSRnA.

• 1 – U2Xn: Double the USART Transmission Speed