From Wikipedia, the free encyclopedia

ECC DIMMs typically have nine memory chips on each side, one more than usually found on non-ECC DIMMs (some modules may have 5 or 18).[1]

Error correction code memory (ECC memory) is a type of computer data storage that uses an error correction code[a] (ECC) to detect and correct n-bit data corruption which occurs in memory. ECC memory is used in most computers where data corruption cannot be tolerated, like industrial control applications, critical databases, and infrastructural memory caches.

Typically, ECC memory maintains a memory system immune to single-bit errors: the data that is read from each word is always the same as the data that had been written to it, even if one of the bits actually stored has been flipped to the wrong state. Most non-ECC memory cannot detect errors, although some non-ECC memory with parity support allows detection but not correction.

Description[edit]

Error correction codes protect against undetected data corruption and are used in computers where such corruption is unacceptable, examples being scientific and financial computing applications, or in database and file servers. ECC can also reduce the number of crashes in multi-user server applications and maximum-availability systems.

Electrical or magnetic interference inside a computer system can cause a single bit of dynamic random-access memory (DRAM) to spontaneously flip to the opposite state. It was initially thought that this was mainly due to alpha particles emitted by contaminants in chip packaging material, but research has shown that the majority of one-off soft errors in DRAM chips occur as a result of background radiation, chiefly neutrons from cosmic ray secondaries, which may change the contents of one or more memory cells or interfere with the circuitry used to read or write to them.[2] Hence, the error rates increase rapidly with rising altitude; for example, compared to sea level, the rate of neutron flux is 3.5 times higher at 1.5 km and 300 times higher at 10-12 km (the cruising altitude of commercial airplanes).[3] As a result, systems operating at high altitudes require special provisions for reliability.

As an example, the spacecraft Cassini–Huygens, launched in 1997, contained two identical flight recorders, each with 2.5 gigabits of memory in the form of arrays of commercial DRAM chips. Due to built-in EDAC functionality, the spacecraft’s engineering telemetry reported the number of (correctable) single-bit-per-word errors and (uncorrectable) double-bit-per-word errors. During the first 2.5 years of flight, the spacecraft reported a nearly constant single-bit error rate of about 280 errors per day. However, on November 6, 1997, during the first month in space, the number of errors increased by more than a factor of four on that single day. This was attributed to a solar particle event that had been detected by the satellite GOES 9.[4]

There was some concern that as DRAM density increases further, and thus the components on chips get smaller, while operating voltages continue to fall, DRAM chips will be affected by such radiation more frequently, since lower-energy particles will be able to change a memory cell’s state.[3] On the other hand, smaller cells make smaller targets, and moves to technologies such as SOI may make individual cells less susceptible and so counteract, or even reverse, this trend. Recent studies[5] show that single-event upsets due to cosmic radiation have been dropping dramatically with process geometry and previous concerns over increasing bit cell error rates are unfounded.

Research[edit]

Work published between 2007 and 2009 showed widely varying error rates with over 7 orders of magnitude difference, ranging from 10−10 error/bit·h (roughly one bit error per hour per gigabyte of memory) to 10−17 error/bit·h (roughly one bit error per millennium per gigabyte of memory).[5][6][7] A large-scale study based on Google’s very large number of servers was presented at the SIGMETRICS/Performance ’09 conference.[6] The actual error rate found was several orders of magnitude higher than the previous small-scale or laboratory studies, with between 25,000 (2.5 × 10−11 error/bit·h) and 70,000 (7.0 × 10−11 error/bit·h, or 1 bit error per gigabyte of RAM per 1.8 hours) errors per billion device hours per megabit. More than 8% of DIMM memory modules were affected by errors per year.

The consequence of a memory error is system-dependent. In systems without ECC, an error can lead either to a crash or to corruption of data; in large-scale production sites, memory errors are one of the most-common hardware causes of machine crashes.[6] Memory errors can cause security vulnerabilities.[6] A memory error can have no consequences if it changes a bit which neither causes observable malfunctioning nor affects data used in calculations or saved. A 2010 simulation study showed that, for a web browser, only a small fraction of memory errors caused data corruption, although, as many memory errors are intermittent and correlated, the effects of memory errors were greater than would be expected for independent soft errors.[8]

Some tests conclude that the isolation of DRAM memory cells can be circumvented by unintended side effects of specially crafted accesses to adjacent cells. Thus, accessing data stored in DRAM causes memory cells to leak their charges and interact electrically, as a result of high cell density in modern memory, altering the content of nearby memory rows that actually were not addressed in the original memory access. This effect is known as row hammer, and it has also been used in some privilege escalation computer security exploits.[9][10]

An example of a single-bit error that would be ignored by a system with no error-checking, would halt a machine with parity checking, or would be invisibly corrected by ECC: a single bit is stuck at 1 due to a faulty chip, or becomes changed to 1 due to background or cosmic radiation; a spreadsheet storing numbers in ASCII format is loaded, and the character «8» (decimal value 56 in the ASCII encoding) is stored in the byte that contains the stuck bit at its lowest bit position; then, a change is made to the spreadsheet and it is saved. As a result, the «8» (0011 1000 binary) has silently become a «9» (0011 1001).

Solutions[edit]

Several approaches have been developed to deal with unwanted bit-flips, including immunity-aware programming, RAM parity memory, and ECC memory.

This problem can be mitigated by using DRAM modules that include extra memory bits and memory controllers that exploit these bits. These extra bits are used to record parity or to use an error-correcting code (ECC). Parity allows the detection of all single-bit errors (actually, any odd number of wrong bits). The most-common error correcting code, a single-error correction and double-error detection (SECDED) Hamming code, allows a single-bit error to be corrected and (in the usual configuration, with an extra parity bit) double-bit errors to be detected. Chipkill ECC is a more effective version that also corrects for multiple bit errors, including the loss of an entire memory chip.

Implementations[edit]

In 1982 this 512KB memory board from Cromemco used 22 bits of storage per 16 bit word to allow for single-bit error correction

Seymour Cray famously said «parity is for farmers» when asked why he left this out of the CDC 6600.[11] Later, he included parity in the CDC 7600, which caused pundits to remark that «apparently a lot of farmers buy computers». The original IBM PC and all PCs until the early 1990s used parity checking.[12] Later ones mostly did not.

An ECC-capable memory controller can generally[a] detect and correct errors of a single bit per word[b] (the unit of bus transfer), and detect (but not correct) errors of two bits per word. The BIOS in some computers, when matched with operating systems such as some versions of Linux, BSD, and Windows (Windows 2000 and later[13]), allows counting of detected and corrected memory errors, in part to help identify failing memory modules before the problem becomes catastrophic.

Some DRAM chips include «internal» on-chip error correction circuits, which allow systems with non-ECC memory controllers to still gain most of the benefits of ECC memory.[14][15] In some systems, a similar effect may be achieved by using EOS memory modules.

Error detection and correction depends on an expectation of the kinds of errors that occur. Implicitly, it is assumed that the failure of each bit in a word of memory is independent, resulting in improbability of two simultaneous errors. This used to be the case when memory chips were one-bit wide, what was typical in the first half of the 1980s; later developments moved many bits into the same chip. This weakness is addressed by various technologies, including IBM’s Chipkill, Sun Microsystems’ Extended ECC, Hewlett Packard’s Chipspare, and Intel’s Single Device Data Correction (SDDC).

DRAM memory may provide increased protection against soft errors by relying on error correcting codes. Such error-correcting memory, known as ECC or EDAC-protected memory, is particularly desirable for high fault-tolerant applications, such as servers, as well as deep-space applications due to increased radiation. Some systems also «scrub» the memory, by periodically reading all addresses and writing back corrected versions if necessary to remove soft errors.

Interleaving allows for distribution of the effect of a single cosmic ray, potentially upsetting multiple physically neighboring bits across multiple words by associating neighboring bits to different words. As long as a single event upset (SEU) does not exceed the error threshold (e.g., a single error) in any particular word between accesses, it can be corrected (e.g., by a single-bit error correcting code), and an effectively error-free memory system may be maintained.[16]

Error-correcting memory controllers traditionally use Hamming codes, although some use triple modular redundancy (TMR). The latter is preferred because its hardware is faster than that of Hamming error correction scheme.[16] Space satellite systems often use TMR,[17][18][19] although satellite RAM usually uses Hamming error correction.[20]

Many early implementations of ECC memory mask correctable errors, acting «as if» the error never occurred, and only report uncorrectable errors. Modern implementations log both correctable errors (CE) and uncorrectable errors (UE). Some people proactively replace memory modules that exhibit high error rates, in order to reduce the likelihood of uncorrectable error events.[21]

Many ECC memory systems use an «external» EDAC circuit between the CPU and the memory. A few systems with ECC memory use both internal and external EDAC systems; the external EDAC system should be designed to correct certain errors that the internal EDAC system is unable to correct.[14] Modern desktop and server CPUs integrate the EDAC circuit into the CPU,[22] even before the shift toward CPU-integrated memory controllers, which are related to the NUMA architecture. CPU integration enables a zero-penalty EDAC system during error-free operation.

As of 2009, the most-common error-correction codes use Hamming or Hsiao codes that provide single-bit error correction and double-bit error detection (SEC-DED). Other error-correction codes have been proposed for protecting memory – double-bit error correcting and triple-bit error detecting (DEC-TED) codes, single-nibble error correcting and double-nibble error detecting (SNC-DND) codes, Reed–Solomon error correction codes, etc. However, in practice, multi-bit correction is usually implemented by interleaving multiple SEC-DED codes.[23][24]

Early research attempted to minimize the area and delay overheads of ECC circuits. Hamming first demonstrated that SEC-DED codes were possible with one particular check matrix. Hsiao showed that an alternative matrix with odd weight columns provides SEC-DED capability with less hardware area and shorter delay than traditional Hamming SEC-DED codes. More recent research also attempts to minimize power in addition to minimizing area and delay.[25][26][27]

Cache[edit]

Many CPUs use error-correction codes in the on-chip cache, including the Intel Itanium, Xeon, Core and Pentium (since P6 microarchitecture)[28][29] processors, the AMD Athlon, Opteron, all Zen-[30] and Zen+-based[31] processors (EPYC, EPYC Embedded, Ryzen and Ryzen Threadripper), and the DEC Alpha 21264.[23][32]

As of 2006, EDC/ECC and ECC/ECC are the two most-common cache error-protection techniques used in commercial microprocessors. The EDC/ECC technique uses an error-detecting code (EDC) in the level 1 cache. If an error is detected, data is recovered from ECC-protected level 2 cache. The ECC/ECC technique uses an ECC-protected level 1 cache and an ECC-protected level 2 cache.[33] CPUs that use the EDC/ECC technique always write-through all STOREs to the level 2 cache, so that when an error is detected during a read from the level 1 data cache, a copy of that data can be recovered from the level 2 cache.

Registered memory[edit]

Registered, or buffered, memory is not the same as ECC; the technologies perform different functions. It is usual for memory used in servers to be both registered, to allow many memory modules to be used without electrical problems, and ECC, for data integrity. Memory used in desktop computers is usually neither, for economy. However, unbuffered (not-registered) ECC memory is available,[34] and some non-server motherboards support ECC functionality of such modules when used with a CPU that supports ECC.[35] Registered memory does not work reliably in motherboards without buffering circuitry, and vice versa.

Advantages and disadvantages[edit]

Ultimately, there is a trade-off between protection against unusual loss of data and a higher cost.

ECC memory usually involves a higher price when compared to non-ECC memory, due to additional hardware required for producing ECC memory modules, and due to lower production volumes of ECC memory and associated system hardware. Motherboards, chipsets and processors that support ECC may also be more expensive.

ECC support varies among motherboard manufacturers so ECC memory may simply not be recognized by a ECC-incompatible motherboard. Most motherboards and processors for less critical applications are not designed to support ECC. Some ECC-enabled boards and processors are able to support unbuffered (unregistered) ECC, but will also work with non-ECC memory; system firmware enables ECC functionality if ECC memory is installed.

ECC may lower memory performance by around 2–3 percent on some systems, depending on the application and implementation, due to the additional time needed for ECC memory controllers to perform error checking.[36] However, modern systems integrate ECC testing into the CPU, generating no additional delay to memory accesses as long as no errors are detected.[22][37][38]

ECC supporting memory may contribute to additional power consumption due to error correcting circuitry.

Notes[edit]

- ^ a b Most ECC memory uses a SECDED code.

- ^ While 72-bit word with 64 data bits and 8 checking bits are common, ECC is also used with smaller and larger sizes.

References[edit]

- ^ Werner Fischer. «RAM Revealed». admin-magazine.com. Retrieved October 20, 2014.

- ^ Single Event Upset at Ground Level, Eugene Normand, Member, IEEE, Boeing Defense & Space Group, Seattle, WA 98124-2499

- ^ a b «A Survey of Techniques for Modeling and Improving Reliability of Computing Systems», IEEE TPDS, 2015

- ^ Gary M. Swift and Steven M. Guertin. «In-Flight Observations of Multiple-Bit Upset in DRAMs». Jet Propulsion Laboratory

- ^ a b Borucki, «Comparison of Accelerated DRAM Soft Error Rates Measured at Component and System Level», 46th Annual International Reliability Physics Symposium, Phoenix, 2008, pp. 482–487

- ^ a b c d Schroeder, Bianca; Pinheiro, Eduardo; Weber, Wolf-Dietrich (2009). DRAM Errors in the Wild: A Large-Scale Field Study (PDF). SIGMETRICS/Performance. ACM. ISBN 978-1-60558-511-6.

- Robin Harris (October 4, 2009). «DRAM error rates: Nightmare on DIMM street». ZDNet.

- ^ «A Memory Soft Error Measurement on Production Systems». Archived from the original on 2017-02-14. Retrieved 2011-06-27.

- ^ Li, Huang; Shen, Chu (2010). ««A Realistic Evaluation of Memory Hardware Errors and Software System Susceptibility». Usenix Annual Tech Conference 2010″ (PDF).

- ^ Yoongu Kim; Ross Daly; Jeremie Kim; Chris Fallin; Ji Hye Lee; Donghyuk Lee; Chris Wilkerson; Konrad Lai; Onur Mutlu (2014-06-24). «Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors» (PDF). ece.cmu.edu. IEEE. Retrieved 2015-03-10.

- ^ Dan Goodin (2015-03-10). «Cutting-edge hack gives super user status by exploiting DRAM weakness». Ars Technica. Retrieved 2015-03-10.

- ^ «CDC 6600». Microsoft Research. Retrieved 2011-11-23.

- ^ «Parity Checking». Pcguide.com. 2001-04-17. Retrieved 2011-11-23.

- ^ DOMARS. «mca — Windows drivers». docs.microsoft.com. Retrieved 2021-03-27.

- ^ a b

A. H. Johnston. «Space Radiation Effects in Advanced Flash Memories» Archived 2016-03-04 at the Wayback Machine. NASA Electronic Parts and Packaging Program (NEPP). 2001. - ^ «ECC DRAM – Intelligent Memory». intelligentmemory.com. Archived from the original on 2019-02-12. Retrieved 2021-06-12.

- ^ a b «Using StrongArm SA-1110 in the On-Board Computer of Nanosatellite». Tsinghua Space Center, Tsinghua University, Beijing. Archived from the original on 2011-10-02. Retrieved 2009-02-16.

- ^ «Actel engineers use triple-module redundancy in new rad-hard FPGA». Military & Aerospace Electronics. Archived from the original on 2012-07-14. Retrieved 2009-02-16.

- ^ «SEU Hardening of Field Programmable Gate Arrays (FPGAs) For Space Applications and Device Characterization». Klabs.org. 2010-02-03. Archived from the original on 2011-11-25. Retrieved 2011-11-23.

- ^ «FPGAs in Space». Techfocusmedia.net. Retrieved 2011-11-23.[permanent dead link]

- ^ «Commercial Microelectronics Technologies for Applications in the Satellite Radiation Environment». Radhome.gsfc.nasa.gov. Archived from the original on 2001-03-04. Retrieved 2011-11-23.

- ^

Doug Thompson, Mauro Carvalho Chehab.

«EDAC — Error Detection And Correction» Archived 2009-09-05 at the Wayback Machine.

2005 — 2009.

«The ‘edac’ kernel module goal is to detect and report errors that occur

within the computer system running under linux.» - ^ a b «AMD-762™ System Controller Software/BIOS Design Guide, p. 179» (PDF).

- ^ a b Doe Hyun Yoon; Mattan Erez. «Memory Mapped ECC: Low-Cost Error Protection for Last Level Caches». 2009. p. 3

- ^ Daniele Rossi; Nicola Timoncini; Michael Spica; Cecilia Metra.

«Error Correcting Code Analysis for Cache Memory High Reliability and Performance» Archived 2015-02-03 at the Wayback Machine. - ^ Shalini Ghosh; Sugato Basu; and Nur A. Touba. «Selecting Error Correcting Codes to Minimize Power in Memory Checker Circuits» Archived 2015-02-03 at the Wayback Machine. p. 2 and p. 4.

- ^ Chris Wilkerson; Alaa R. Alameldeen; Zeshan Chishti; Wei Wu; Dinesh Somasekhar; Shih-lien Lu. «Reducing cache power with low-cost, multi-bit error-correcting codes». doi:10.1145/1816038.1815973.

- ^ M. Y. Hsiao. «A Class of Optimal Minimum Odd-weight-column SEC-DED Codes». 1970.

- ^

Intel Corporation.

«Intel Xeon Processor E7 Family: Reliability, Availability, and Serviceability».

2011.

p. 12. - ^ «Bios and Cache — Custom Build Computers». www.custom-build-computers.com. Retrieved 2021-03-27.

- ^ «AMD Zen microarchitecture — Memory Hierarchy». WikiChip. Retrieved 15 October 2018.

- ^ «AMD Zen+ microarchitecture — Memory Hierarchy». WikiChip. Retrieved 15 October 2018.

- ^

Jangwoo Kim; Nikos Hardavellas; Ken Mai; Babak Falsafi; James C. Hoe.

«Multi-bit Error Tolerant Caches Using Two-Dimensional Error Coding».

2007.

p. 2. - ^

Nathan N. Sadler and Daniel J. Sorin.

«Choosing an Error Protection Scheme for a Microprocessor’s L1 Data Cache».

2006.

p. 1. - ^ «Typical unbuffered ECC RAM module: Crucial CT25672BA1067».

- ^ Specification of desktop motherboard that supports both ECC and non-ECC unbuffered RAM with compatible CPUs

- ^ «Discussion of ECC on pcguide». Pcguide.com. 2001-04-17. Retrieved 2011-11-23.

- ^ Benchmark of AMD-762/Athlon platform with and without ECC Archived 2013-06-15 at the Wayback Machine

- ^ «ECCploit: ECC Memory Vulnerable to Rowhammer Attacks After All». Systems and Network Security Group at VU Amsterdam. Retrieved 2018-11-22.

External links[edit]

- SoftECC: A System for Software Memory Integrity Checking

- A Tunable, Software-based DRAM Error Detection and Correction Library for HPC

- Detection and Correction of Silent Data Corruption for Large-Scale High-Performance Computing

- Single-Bit Errors: A Memory Module Supplier’s perspective on cause, impact and detection

- Intel Xeon Processor E3 — 1200 Product Family Memory Configuration Guide

- Linus Torvalds On The Importance Of ECC RAM, Calls Out Intel’s «Bad Policies» Over ECC

ECC, от английского error-correcting code, переводиться на русский язык, как код коррекции ошибок. Встроенная в контроллёры флешек технология, обнаружения и исправления ошибок при передаче данных. ECC способна справиться только с несущественными проблемами, в тяжелых случаях флешка заблокируется на запись данных.

ЗАЧЕМ ЭТО НАДО

Если в эпоху качественных SLC и MLC микросхем флэш-памяти, не было особого смысла обращать внимание на этот механизм исправления ошибок. То сейчас когда в подавляющем количестве флешек, установлена или банально TLC-память или какая-нибудь MLC DownGrade, не стоит пренебрегать настройками ECC-механизма.

Данная технология позволяет продлить жизнь флешки до следующих затыков с ней, ведь не хочется, каждый месяц заново перепрошивать свою флешку.

Еще одной положительной чертой, является вероятность достижения максимального возможного объёма флэш-диска. Он может быть даже выше, чем изначально имел носитель, особенно у флешек с отбракованными микросхемами.

НЕДОСТАТКИ

Чем выше вы установите значение ECC-параметра, тем большую нагрузку он создаст на контроллёр флешки. А это в свою очередь, может негативно сказаться на её производительность, т.е. скорость работы. Также из заметных недостатков, высокой нагрузки, это больший разогрев флешки.

РЕКОМЕНДУЕМЫЕ ЗНАЧЕНИЯ ПАРАМЕТРА ECC

В большинстве утилитах, используется не применяемые в флэш-листах значения (например: 7b/512B и 72b/1K), а суммы определенных параметров. Как правило, в диапазоне равеном от 0 до 15, в некоторых производственных программах, ввиду поддержки крайне некачественной памяти, от 0 до 20. Для посетителей проекта USBDev.ru, я составил следующую таблицу.

| ECC Value | |

|---|---|

| MEMORY TYPE: | ECC: |

| SLC | 1 |

| MLC 32nm, 35nm, 42nm, 50nm, … | 3-4 |

| MLC 24nm, 25nm, 26nm, 32nm | 4-8 |

| MLC 21nm, 20nm, 19nm, … | 8-12 |

| TLC 27nm, 32nm, 43nm, … | 8 |

| TLC 24nm, 21nm, 19nm, … | 12-15 |

В некоторых утилитах, используется другая система координат, к примеру производственный комплекс Dyna для контроллёров SMI. На этот случай, чуть ниже можно обнаружить ссылку на особености настроек у конкретных производителей.

Немного поясню, как следует использовать таблицу данную выше. Так вот, если ваша флешка добротная (хорошо зарекомендовавший себя бренд), то выбирайте минимальное значение из неё. Для подарочных и поддельных флешек, настоятельно советую использовать максимальное значение параметра ECC, для своего типа памяти.

РЕАЛИЗАЦИЯ В ПРОИЗВОДСТВЕННЫХ УТИЛИТАХ

Далеко не во всех утилит, имеется возможность ручной корректировки ECC-опции. Можно сказать что ECC, это такая фитча Sorting-составляющей производственных утилит. Попробую кратко выразить это в таблице, для основных производителей USB-контроллёров.

| ECC Compatible Software | |

|---|---|

| Company: | Tools: |

| ALCOR | AlcorMP_UFD FC MpTool AAMP |

| CHIPSBANK | Chipsbank UMPTool CBM2093 UMPTool CBM2098 UMPTool umptool209X V68 Building Tools |

| INNOSTOR | Innostor MPTool Innostor 917 LFA MP Tool |

| PHISON | UPTool UP19_CTool UP21_CTool UP23_CTool |

| SILICON GO | KingStore Manufacture Tool SiliconGo MPTools SiliconGo MPTool2 |

| SKYMEDI | SK6221 MPTool |

| SMI | Dyna Mass Storage Production Tool |

| СТАТЬИ НА ТЕМУ ECC-КОРРЕКЦИИ | ||

|---|---|---|

| ECC значения для контроллёров Alcor с DownGrade памятью | 2015 | |

| Настройка ECC у контроллёров Silicon Motion (SMI) | 2015 | |

Для ваших вопросов, на проекте USBDev существует форум – FORUM.

Всем привет! Тема сегодняшней публикации — поддержка ECC оперативной памяти: что это такое, как работает данная функция, зависит ли от процессора ее использование на ПК.

Что такое ЕСС память

Аббревиатура происходит от английского названия error correcting code memory, то есть память с коррекцией ошибок кода. Такая ОЗУ распознает и устраняет спонтанно возникающие изменения в битах памяти, которых быть не должно.

Как правило, такая память может исправить изменения в одном бите одного машинного слова. При его чтении будет опознано то же значение, что и было записано, несмотря на возникающие «глюки».

Обычная память, то есть non-ECC, этого делать не умеет.

Этот тип памяти используется в компьютерах, для которых важна бесперебойная работа, включая крупные серверные станции. Для использования такого режима необходима поддержка контроллером ОЗУ – как встраиваемого в чипсет, так и реализованном на кристалле вместе с ядрами.

Базовый алгоритм, который используется чаще всего, основан на коде Хемминга – самоконтролирующемся двоичном коде, названном в честь предложившего такую систему американского математика.

Существуют алгоритмы, способные исправлять более одной ошибки, но используются они реже. С технологической точки зрения такая система предполагает использование модулей ОЗУ, в которых на каждые 8 микросхем памяти приходится один компонент, хранящий ЕСС-коды (то есть 8 бит на каждые 64 бита).

Причины появления ошибок в ОЗУ

Главная проблема для любого электронного устройства – невидимые космические лучи, от которых земная атмосфера не защищает должным образом. Элементарные частицы, которые пребывают в этом потоке, способны влиять на работу электроники.

А так как любой компьютер на самом «глубинном» уровне проводит все вычисления с помощью двоичных кодов, нарушения свойств электронных компонентов и провоцируют ошибки в работе.

Характерно, что чем выше от уровня моря, тем меньше плотность воздуха и соответственно, интенсивнее космическое излучение. Компьютерные системы, которые работают на большой высоте, требуют более эффективной защиты. Советую также почитать «Что такое ОЗУ в компьютере: из чего состоит и для чего служит?»(уже на сайте).

Стоит ли использовать ЕСС память

Объективных причин для использования такой ОЗУ на домашнем ПК нет.

Несмотря на то, что земной диск медленно дрейфует по Космическому океану, покоясь на спинах трех китов, вероятность искажения данных под воздействием вредоносных лучей, на самом-то деле крайне мала. При этом самое страшное, что может случиться при таких неполадках – вылет операционной системы в синий экран.

Впрочем, это может быть действительно страшно – например, в случае, если вы в течение пары часов монтировали видеоролик, забывая сохраняться в процессе, или же у вас последний и решительный бой, от которого зависит судьба клана, в какой-нибудь ММОРПГ.

Такая память работает медленнее обычной – в среднем, на 2-3%, так как для проверки контрольных сумм необходим один дополнительный такт контроллера. Такой режим работы требует больше логических ресурсов.

Как уже сказано выше, в основном такая память почти всегда регистровая (Registered), то есть имеет дополнительный регистр для считывания и хранения двоичных кодов. Существуют модули ECC памяти без регистров (UDIMM), которые можно использовать в домашних ПК.

Однако учтите, что такое удовольствие обойдется дороже, так как цена на такие модули ОЗУ обычно выше. Кроме того, требуется наличие материнской платы, чипсета и процессора (к слову, такие модели есть и у Intel, и у AMD), поддерживающих ЕСС память. Стоят они внезапно тоже, как правило, дороже.

И если вы решили проапгрейдить комп для использования ЕСС памяти, проверьте спецификации упомянутых выше компонентов. Если в описании написано что нет поддержки такого режима, деталь придется менять на более подходящую, что значит дополнительные расходы.

Не исключено, что придется менять и мать, и «камень», и планки оперативки. При сборке нового компьютера несколько проще: можно сразу купить соответствующие компоненты. Однако, на мой взгляд, это уже лишнее – страховка от мнимых сбоев не стоит потери быстродействия.

Также советую на эту тему ознакомиться с публикациями «Влияние тактовой частоты оперативной памяти в компьютере»(уже на блоге) и «Тайминги и частота оперативной памяти: кто важнее и влиятельней?». Буду признателен всем, кто расшарит эту статью в социальных сетях. До завтра!

С уважением, автор блога Андрей Андреев.

Оглавление

- Вступление

- Коррекция ошибок

- Финансовая сторона

- Тестовый стенд

- Методика тестирования

- Результаты тестирования

- Тест памяти

- 3DMark

- 7Zip

- Cinebench

- CrystalMark

- Fritz

- LinX

- wPrime

- AIDA64 Extreme

- Заключение

Вступление

На сегодняшний день на просторах Рунета можно встретить открытые темы на форумах с вопросами – стоит ли брать рабочую станцию с ECC-памятью или можно обойтись обычной? В данных ветках можно прочесть множество противоречивых утверждений, и часть из них говорит о том, что коррекция ошибок сильно замедляет память, а следовательно и ЦП. Но мало кто это проверял на деле на современных процессорах.

Сегодня мы разберемся в этом вопросе и сравним производительность серверного процессора с обоими типами памяти. Но для начала небольшой экскурс.

Коррекция ошибок

Для чего необходима коррекция? И почему в работе памяти возникают ошибки? Перед ответом на эти вопросы следует разделить ошибки на два типа:

- Аппаратные ошибки;

- Случайные ошибки.

Причиной появления аппаратных ошибок является дефектная микросхема DRAM, а случайные ошибки возникают под воздействием излучения, альфа-частиц, элементарных частиц и прочего. Соответственно, первые в принципе неисправимы – если чип дефектный, то поможет только его замена; а вот вторые могут быть исправлены.

Почему же так необходима коррекция ошибок в рабочих станциях и серверах? Однобитовая ошибка в 64-битном слове меняет содержимое ячейки памяти, а в конечном итоге на жесткий диск может быть записано другое число, другие данные, при этом компьютер не зафиксирует эту подмену. А изменение бита в оперативной памяти может вызвать сбой программы, что для рабочей станции и сервера недопустимо.

рекомендации

-17% на RTX 4070 Ti в Ситилинке

Выбираем игровой ноут: на что смотреть, на чем сэкономить

3080 дешевле 70 тр — цены снова пошли вниз

Ищем PHP-программиста для апгрейда конфы

3070 Gainward Phantom дешевле 50 тр

13700K дешевле 40 тр в Регарде

16 видов <b>4070 Ti</b> в Ситилинке — все до 100 тр

3070 Ti дешевле 60 тр в Ситилинке

3070 Gigabyte Gaming за 50 тр с началом

Компьютеры от 10 тр в Ситилинке

3070 дешевле 50 тр в Ситилинке

MSI 3050 за 25 тр в Ситилинке

3060 Gigabyte Gaming за 30 тр с началом

13600K дешевле 30 тр в Регарде

4080 почти за 100тр — дешевле чем по курсу 60

-19% на 13900KF — цены рухнули

12900K за 40тр с началом в Ситилинке

RTX 4090 за 140 тр в Регарде

3060 Ti Gigabyte за 42 тр в Регарде

Для обнаружения изменения битов памяти можно использовать метод подсчета контрольной суммы, но он позволяет лишь обнаруживать ошибки без их исправления.

В свое время было предложено много различных способов решения данной проблемы, но на сегодняшний день наибольшее распространение получил метод коррекции ошибок или ECC (Error-Correcting Code). Данный метод позволяет автоматически исправлять однобитовые ошибки в 64-битном слове – SEC (Single Error Correction) и детектировать двухбитовые – DED (Double Error Detection).

Физическая реализация ECC заключается в размещении дополнительной микросхемы памяти на модуле ОЗУ – соответственно, при одностороннем дизайне модуля памяти вместо восьми чипов располагается девять, а при двустороннем вместо шестнадцати – восемнадцать. Таким образом, ширина модуля становится не 64 бита, а 72 бита.

Метод коррекции ошибок работает следующим образом: при записи 64 бит данных в ячейку памяти происходит подсчет контрольной суммы, составляющей 8 бит. Когда процессор обращается к этим данным и производит считывание, проводится повторный подсчет контрольной суммы и сравнение с исходной. Если суммы не совпадают – произошла ошибка. Если она однобитовая, то неправильный бит исправляется автоматически, если двухбитовая – детектируется и сообщается ОС.

Финансовая сторона

Прежде чем приступить к тестированию, необходимо затронуть финансовый вопрос.

Стоимость обычного модуля памяти DDR3-1600 с напряжением 1.35 В и объемом 8 Гбайт составляет около 3600 рублей, а с коррекцией ошибок – 4800 рублей. На первый взгляд ECC-память выходит на 30-35% дороже, что, в целом, не позволяет их сравнивать в силу существенно большей стоимости последней. Но почему же тогда такой вопрос возникает при сборке рабочей станции? Все просто – необходимо смотреть на данный вопрос шире, а именно – смотреть на общую стоимость рабочей станции.

Ценник однопроцессорной станции на базе четырехъядерного восьмипоточного Xeon (настольные процессоры серий i5 и i7 не поддерживают ECC-память) с 32 Гбайтами памяти, материнской платы с чипсетом C222/С224/С226 (десктопные наборы логики Z87/Z97 и другие также не поддерживают память с коррекцией ошибок) будет превышать 70 000 рублей (при условии, что устанавливаются серверные SSD с повышенным ресурсом). А если включить в эту стоимость и дискретную видеокарту, и прочие сопутствующие компоненты, например, ИБП, то ценник из пятизначного превратится в шестиизначный, перевалив планку в 100 000 рублей.

Покупка 32 Гбайт памяти с коррекцией ошибок потребует дополнительных 4-6 тысяч рублей, что по отношению к общей стоимости рабочей станции не превышает 5%, то есть не является критичным. Также переход от десктопного к серверному железу предоставит и другие преимущества, например: интегрированные графические карты P4600 в процессорах Intel Xeon E3-1200 третьего поколения получили оптимизированные драйверы, которые должны повышать производительность в профессиональных приложениях, например, в CAD; поддержка технологии Intel VT-d, которая позволяет пробрасывать устройства в виртуальную среду, например, видеокарты; прочие серверные технологии – Intel AMT или IPMI, WatchDog и другие, которые также могут оказаться полезными.

Таким образом, хоть и сама ECC-память стоит заметно дороже обычной, в общей стоимости рабочей станции данная статья затрат является несущественной, и переплата не превышает 5%.

Тестовый стенд

Для данного обзора использовалась следующая конфигурация:

- Материнская плата: Supermicro X10SAE (Intel C226, LGA 1150);

- Процессор: Xeon E3-1245V3 (Turbo Boost – off, EIST – off, HT – on);

- Оперативная память:

- 2x Kingston DDR3-1600 ECC 8 Гбайт (KVR16LE11/8 CL11, 1.35 В);

- 2x Kingston DDR3-1600 8 Гбайт (KVR16LN11/8 CL11, 1.35 В);

- ОС: Windows 8.1 Pro 64-bit.

Методика тестирования

В рамках тестирования были произведены замеры производительности как при одноканальном режиме работы ИКП, так и при двухканальном. Суммарный объем ОЗУ составил 8 (один модуль) и 16 Гбайт (два модуля) соответственно.

Программное обеспечение:

- 3DMark 2006 1.2;

- 7Zip 9.20;

- AIDA64 Extreme 5.20.3400;

- Cinebench R15;

- CrystalMark 2004R3;

- Fritz 4.20;

- LinX 0.6.5;

- wPrime 2.10.

Результаты тестирования

Тест памяти

Перед тем, как приступить к тестированию, проведем замер пропускной способности памяти и латентности.

При изучении результатов можно заключить, что производительность ECC- и non-ECC- памяти находится на одном и том же уровне в рамках погрешности.

Если в предыдущем тесте от замера к замеру выигрывал то один, то другой тип памяти, то при замере латентности ECC-память постоянно показывает большие задержки. Но разница несущественна – всего лишь 1 нс.

Таким образом, замер ПС и латентности памяти не показал особых различий между ECC- и non-ECC-памятью. Посмотрим, повторится ли это в последующих тестах.

3DMark

Тестовый пакет 3DMark содержит подтесты как для процессора, так и для графической карты. Здесь и кроется самое интересное – давно известно, что встроенному видеоядру не хватает существующей ПСП в 25.6 Гбайт/с, поэтому именно в графических подтестах можно выявить негативное влияние коррекции ошибок, если оно вообще есть,…

… но разницы нет – что ECC, что non-ECC. Ни процессор, ни интегрированное ядро никак не реагируют на замену обычной памяти на DDR с коррекцией ошибок – результаты одинаковы в рамках погрешности. Среднеарифметическая разница составила 0.02% в пользу ECC-памяти для одноканального режима и 1.6% для двухканального режима.

При этом нельзя сказать, что встроенная видеокарта P4600 не зависит от скорости ОЗУ – при одноканальном доступе общий результат почти на 30% ниже, чем при двухканальном. Другими словами, скорость ОЗУ критична для графического ядра, но сами по себе «ECC-версии» не влияют ни на скорость ОЗУ, ни на видеокарту.

7Zip

Архиваторы, как известно, чувствительны к памяти, поэтому, возможно, здесь получится зафиксировать влияние типа памяти на производительность.

Ситуация с архивацией неоднозначная: с одной стороны – в одноканальном режиме (как при распаковке, так и при сжатии) ECC-память уверенно оказывается медленнее на 2%; с другой – в двухканальном режиме при сжатии ECC-память уверенно быстрее, а при распаковке – медленнее, а среднее арифметическое – быстрее на 0.65%.

Скорее всего, причина в следующем – пропускной способности памяти при одноканальном доступе процессору явно недостаточно, и поэтому чуть большая латентность ECC-памяти сказывается на производительности; а при двухканальном доступе ПСП полностью покрывает нужды CPU и поэтому чуть большая латентность памяти с коррекцией ошибок не сказывается на производительности. В любом случае зафиксировать существенного влияния на скорость архивации не получилось.

Cinebench

Тестовый пакет Cinebench содержит подтест как процессора, так и видеокарты.

Но ни первый, ни вторая никак не отреагировали на ECC-память.

Зато налицо явная зависимость видеокарты от ПСП – при одноканальном доступе результат в OpenGL оказался на 25% ниже, чем при двухканальном. Вспоминая результаты 3DMark и смотря на нынешние, можно заключить, что производительность интегрированной видеокарты хоть и зависит от ПСП, но ECC-память не оказывает на нее негативного влияния.

схема управления ошибками в данных по зашумленным каналам связи

В вычислениях, телекоммуникации, теория информации и теория кодирования, код исправления ошибок, иногда код исправления ошибок, (ECC ) используется для контроля ошибок в данных по ненадежным или зашумленным каналам связи. Основная идея заключается в том, что отправитель кодирует сообщение с помощью избыточной информации в форме ECC. Избыточность позволяет получателю обнаруживать ограниченное количество ошибок, которые могут возникать в любом месте сообщения, и часто исправлять эти ошибки без повторной передачи. Американский математик Ричард Хэмминг был пионером в этой области в 1940-х годах и изобрел первый исправляющий ошибки код в 1950 году: код Хэмминга (7,4).

ECC контрастирует с обнаружением ошибок. в том, что обнаруженные ошибки можно исправить, а не просто обнаружить. Преимущество состоит в том, что системе, использующей ECC, не требуется обратный канал для запроса повторной передачи данных при возникновении ошибки. Обратной стороной является то, что к сообщению добавляются фиксированные накладные расходы, что требует более высокой полосы пропускания прямого канала. Таким образом, ECC применяется в ситуациях, когда повторные передачи являются дорогостоящими или невозможными, например, при односторонних каналах связи и при передаче на несколько приемников в многоадресной передаче. Соединения с длительной задержкой также выигрывают; в случае спутника, вращающегося вокруг Урана, повторная передача из-за ошибок может вызвать задержку в пять часов. Информация ECC обычно добавляется к запоминающим устройствам для восстановления поврежденных данных, широко используется в модемах и используется в системах, где основной памятью является память ECC.

Обработка ЕСС в приемнике может применяться к цифровому потоку битов или к демодуляции несущей с цифровой модуляцией. В последнем случае ECC является неотъемлемой частью начального аналого-цифрового преобразования в приемнике. Декодер Витерби реализует алгоритм мягкого решения для демодуляции цифровых данных из аналогового сигнала, искаженного шумом. Многие кодеры / декодеры ECC также могут генерировать сигнал с коэффициентом ошибок по битам (BER), который можно использовать в качестве обратной связи для точной настройки аналоговой приемной электроники.

Максимальная доля ошибок или отсутствующих битов, которые могут быть исправлены, определяется конструкцией кода ECC, поэтому разные коды исправления ошибок подходят для разных условий. Как правило, более сильный код вызывает большую избыточность, которую необходимо передавать с использованием доступной полосы пропускания, что снижает эффективную скорость передачи данных при одновременном улучшении принимаемого эффективного отношения сигнал / шум. Теорема кодирования с шумом канала из Клод Шеннон отвечает на вопрос о том, какая полоса пропускания остается для передачи данных при использовании наиболее эффективного кода, который сводит вероятность ошибки декодирования к нулю. Это устанавливает границы теоретической максимальной скорости передачи информации канала с некоторым заданным базовым уровнем шума. Однако это доказательство неконструктивно и, следовательно, не дает представления о том, как создать код, обеспечивающий производительность. После многих лет исследований некоторые современные системы ECC сегодня очень близки к теоретическому максимуму.

Содержание

- 1 Прямое исправление ошибок

- 2 Как это работает

- 3 Усреднение шума для уменьшения количества ошибок

- 4 Типы ECC

- 5 Кодовая скорость и компромисс между надежностью и скоростью передачи данных

- 6 Составные коды ECC для повышения производительности

- 7 Проверка четности с низкой плотностью (LDPC)

- 8 Турбо-коды

- 9 Локальное декодирование и тестирование кодов

- 10 Чередование

- 10.1 Пример

- 10.2 Недостатки чередования

- 11 Программное обеспечение для кодов исправления ошибок

- 12 Список кодов исправления ошибок

- 13 См. Также

- 14 Ссылки

- 15 Дополнительная литература

- 16 Внешние ссылки

Прямое исправление ошибок

В электросвязи, теории информации и теории кодирования, прямое исправление ошибок (FEC ) или канальное кодирование — это метод, используемый для контроля ошибок в передаче данных по ненадежным или зашумленным каналам связи. Основная идея заключается в том, что отправитель кодирует сообщение с помощью избыточного способа, чаще всего с помощью ECC.

Избыточность позволяет получателю обнаруживать ограниченное количество ошибок, которые могут возникнуть в любом месте сообщения, и часто исправлять эти ошибки без повторной передачи. FEC дает приемнику возможность исправлять ошибки без необходимости использования обратного канала для запроса повторной передачи данных, но за счет фиксированной более высокой полосы пропускания прямого канала. Поэтому FEC применяется в ситуациях, когда повторные передачи являются дорогостоящими или невозможными, например, при односторонних каналах связи и при передаче на несколько приемников в многоадресной передаче. Информация FEC обычно добавляется к запоминающим устройствам (магнитным, оптическим и твердотельным / флэш-накопителям) для восстановления поврежденных данных, широко используется в модемах, используется в системах, где первичной памятью является память ECC, и в ситуациях широковещательной передачи, когда приемник не имеет возможности запрашивать повторную передачу или это может вызвать значительную задержку. Например, в случае спутника, вращающегося вокруг Урана, повторная передача из-за ошибок декодирования может вызвать задержку не менее 5 часов.

Обработка FEC в приемнике может применяться к цифровому битовому потоку или при демодуляции несущей с цифровой модуляцией. Для последнего FEC является неотъемлемой частью начального аналого-цифрового преобразования в приемнике. Декодер Витерби реализует алгоритм мягкого решения для демодуляции цифровых данных из аналогового сигнала, искаженного шумом. Многие кодеры FEC могут также генерировать сигнал с коэффициентом ошибок по битам (BER), который можно использовать в качестве обратной связи для точной настройки аналоговой приемной электроники.

Максимальная доля ошибок или недостающих битов, которые могут быть исправлены, определяется конструкцией ECC, поэтому разные коды прямого исправления ошибок подходят для разных условий. Как правило, более сильный код вызывает большую избыточность, которую необходимо передавать с использованием доступной полосы пропускания, что снижает эффективную скорость передачи данных при одновременном улучшении принимаемого эффективного отношения сигнал / шум. Теорема кодирования канала с шумом Клода Шеннона отвечает на вопрос о том, какая полоса пропускания остается для передачи данных при использовании наиболее эффективного кода, который обращает вероятность ошибки декодирования в ноль. Это устанавливает границы теоретической максимальной скорости передачи информации канала с некоторым заданным базовым уровнем шума. Его доказательство неконструктивно и, следовательно, не дает понимания того, как создать код, обеспечивающий производительность. Однако после многих лет исследований некоторые передовые системы FEC, такие как полярный код, достигают пропускной способности канала Шеннона при гипотезе кадра бесконечной длины.

Как это работает

ECC достигается путем добавления избыточности к передаваемой информации с использованием алгоритма. Избыточный бит может быть сложной функцией многих исходных информационных битов. Исходная информация может появляться или не появляться буквально в закодированном выводе; коды, которые включают немодифицированный ввод в вывод, являются систематическими, тогда как те, которые не включают, являются несистематическими .

Упрощенный пример ECC — передача каждого бита данных 3 раза, что известно как код повторения (3,1) . Через шумный канал приемник может видеть 8 вариантов вывода, см. Таблицу ниже.

| Получен триплет | Интерпретируется как |

|---|---|

| 000 | 0 (без ошибок) |

| 001 | 0 |

| 010 | 0 |

| 100 | 0 |

| 111 | 1 (без ошибок) |

| 110 | 1 |

| 101 | 1 |

| 011 | 1 |

Это позволяет исправить ошибку в любой из трех выборок «большинством голосов» или «демократическим голосованием». Корректирующая способность этого ECC:

- До 1 бита триплета с ошибкой или

- до 2 битов триплета пропущены (случаи не показаны в таблице).

Хотя прост в реализации и Это широко используемое тройное модульное резервирование является относительно неэффективным ECC. Более совершенные коды ECC обычно проверяют несколько последних десятков или даже несколько последних сотен ранее принятых битов, чтобы определить, как декодировать текущую небольшую группу битов (обычно в группах от 2 до 8 бит).

Усреднение шума для уменьшения ошибок

Можно сказать, что ECC работает посредством «усреднения шума»; поскольку каждый бит данных влияет на многие передаваемые символы, искажение одних символов шумом обычно позволяет извлекать исходные пользовательские данные из других неповрежденных принятых символов, которые также зависят от тех же пользовательских данных.

- Из-за этого эффекта «объединения рисков» цифровые системы связи, использующие ECC, как правило, работают значительно выше определенного минимального отношения сигнал / шум, а не ниже него.

- Эта тенденция «все или ничего» — эффект обрыва — становится более выраженной по мере использования более сильных кодов, которые более близко подходят к теоретическому пределу Шеннона.

- Чередование данных, закодированных с помощью ECC, может уменьшить все или ничего свойства переданных кодов ECC, когда ошибки канала имеют тенденцию возникать в пакетах. Однако у этого метода есть ограничения; его лучше всего использовать для узкополосных данных.

Большинство телекоммуникационных систем используют фиксированный канальный код, рассчитанный на ожидаемый наихудший случай частоты ошибок по битам, а затем вообще не работают если частота ошибок по битам станет еще хуже. Однако некоторые системы адаптируются к данным условиям ошибки канала: некоторые экземпляры гибридного автоматического запроса на повторение используют фиксированный метод ECC, пока ECC может обрабатывать частоту ошибок, затем переключаются на ARQ когда частота ошибок становится слишком высокой; адаптивная модуляция и кодирование использует различные скорости ECC, добавляя больше битов исправления ошибок на пакет, когда в канале более высокие частоты ошибок, или удаляя их, когда они не нужны.

Типы ECC

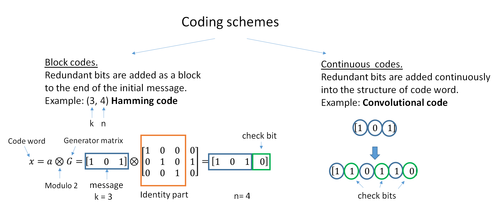

Двумя основными категориями кодов ECC являются блочные коды и сверточные коды.

- Блочные коды работают с блоками фиксированного размера (пакетами) битов или символов заранее определенного размера. Практические блочные коды обычно могут быть жестко декодированы за полиномиальное время до их длины блока.

- Сверточные коды работают с битовыми или символьными потоками произвольной длины. Чаще всего они программно декодируются с помощью алгоритма Витерби, хотя иногда используются и другие алгоритмы. Декодирование Витерби обеспечивает асимптотически оптимальную эффективность декодирования с увеличением длины ограничения сверточного кода, но за счет экспоненциально возрастающей сложности. Завершенный сверточный код также является «блочным кодом» в том смысле, что он кодирует блок входных данных, но размер блока сверточного кода, как правило, произвольный, в то время как блочные коды имеют фиксированный размер, определяемый их алгебраическими характеристиками. Типы завершения для сверточных кодов включают в себя «бит в конце» и «сброс битов».

Существует много типов блочных кодов; Кодирование Рида-Соломона примечательно тем, что оно широко используется в компакт-дисках, DVD и жестких дисках. Другие примеры классических блочных кодов включают Голея, BCH, многомерную четность и коды Хэмминга.

ECC Хэмминга обычно используются для исправления NAND flash ошибки памяти. Это обеспечивает исправление однобитовых ошибок и обнаружение двухбитовых ошибок. Коды Хэмминга подходят только для более надежной одноуровневой ячейки (SLC) NAND. Более плотная многоуровневая ячейка (MLC) NAND может использовать многобитовый корректирующий ECC, такой как BCH или Reed-Solomon. NOR Flash обычно не использует никакого исправления ошибок.

Классические блочные коды обычно декодируются с использованием алгоритмов жесткого решения, что означает, что для каждого входного и выходного сигнала принимается жесткое решение, будет ли он соответствует единице или нулю бит. Напротив, сверточные коды обычно декодируются с использованием алгоритмов мягкого решения, таких как алгоритмы Витерби, MAP или BCJR, которые обрабатывают (дискретизированные) аналоговые сигналы и которые допускают гораздо более высокие ошибки — производительность коррекции, чем декодирование с жестким решением.

Почти все классические блочные коды применяют алгебраические свойства конечных полей. Поэтому классические блочные коды часто называют алгебраическими кодами.

В отличие от классических блочных кодов, которые часто определяют способность обнаружения или исправления ошибок, многие современные блочные коды, такие как коды LDPC, не имеют таких гарантий. Вместо этого современные коды оцениваются с точки зрения их частоты ошибок по битам.

Большинство кодов прямого исправления ошибок исправляют только перевороты битов, но не вставки или удаления битов. В этой настройке расстояние Хэмминга является подходящим способом измерения коэффициента битовых ошибок. Несколько кодов прямого исправления ошибок предназначены для исправления вставки и удаления битов, например, коды маркеров и коды водяных знаков. Расстояние Левенштейна является более подходящим способом измерения частоты ошибок по битам при использовании таких кодов.

Кодовая скорость и компромисс между надежностью и скоростью передачи данных

Фундаментальный принцип ECC состоит в добавлении избыточных битов, чтобы помочь декодеру узнать истинное сообщение, которое было закодировано передатчик. Кодовая скорость данной системы ЕСС определяется как соотношение между количеством информационных битов и общим количеством битов (то есть информацией плюс биты избыточности) в данном коммуникационном пакете. Кодовая скорость, следовательно, является действительным числом. Низкая кодовая скорость, близкая к нулю, подразумевает сильный код, который использует много избыточных битов для достижения хорошей производительности, в то время как большая кодовая скорость, близкая к 1, подразумевает слабый код.

Избыточные биты, защищающие информацию, должны передаваться с использованием тех же коммуникационных ресурсов, которые они пытаются защитить. Это вызывает фундаментальный компромисс между надежностью и скоростью передачи данных. В одном крайнем случае сильный код (с низкой кодовой скоростью) может вызвать значительное увеличение SNR приемника (отношение сигнал / шум), уменьшая частоту ошибок по битам, за счет снижения эффективной скорости передачи данных. С другой стороны, без использования какого-либо ECC (то есть кодовой скорости, равной 1) используется полный канал для целей передачи информации за счет того, что биты остаются без какой-либо дополнительной защиты.

Один интересный вопрос заключается в следующем: насколько эффективным с точки зрения передачи информации может быть ECC, имеющий незначительную частоту ошибок декодирования? На этот вопрос ответил Клод Шеннон с его второй теоремой, которая гласит, что пропускная способность канала — это максимальная скорость передачи данных, достижимая для любого ECC, частота ошибок которого стремится к нулю: его доказательство основано на гауссовском случайном кодировании, которое не подходит для реального мира. Приложения. Верхняя граница, заданная работой Шеннона, вдохновила на долгий путь к разработке ECC, которые могут приблизиться к пределу конечных характеристик. Различные коды сегодня могут достигать почти предела Шеннона. Однако ECC, обеспечивающие пропускную способность, обычно чрезвычайно сложно реализовать.

Наиболее популярные ECC имеют компромисс между производительностью и вычислительной сложностью. Обычно их параметры дают диапазон возможных кодовых скоростей, которые можно оптимизировать в зависимости от сценария. Обычно эта оптимизация выполняется для достижения низкой вероятности ошибки декодирования при минимальном влиянии на скорость передачи данных. Другим критерием оптимизации кодовой скорости является уравновешивание низкой частоты ошибок и количества повторных передач с учетом энергетических затрат на связь.

Составные коды ECC для повышения производительности

Классические (алгебраические) блочные коды а сверточные коды часто комбинируются в схемах конкатенированного кодирования, в которых сверточный код, декодированный по Витерби с короткой ограниченной длиной, выполняет большую часть работы, а блочный код (обычно Рида-Соломона) с большим размером символа и длиной блока «стирает» любые ошибки, сделанные сверточным декодером. Однопроходное декодирование с использованием этого семейства кодов с исправлением ошибок может дать очень низкий уровень ошибок, но для условий передачи на большие расстояния (например, в глубоком космосе) рекомендуется итеративное декодирование.

Составные коды были стандартной практикой в спутниковой связи и связи в дальнем космосе с тех пор, как «Вояджер-2 » впервые применил эту технику во время встречи с Ураном в 1986 году. Аппарат Galileo использовал итеративные конкатенированные коды для компенсации условий очень высокой частоты ошибок, вызванных отказом антенны.

Проверка на четность с низкой плотностью (LDPC)

Коды с проверкой на четность с низкой плотностью (LDPC) — это класс высокоэффективных линейных блочных кодов, созданных из множества кодов одиночной проверки на четность (SPC). Они могут обеспечить производительность, очень близкую к пропускной способности канала (теоретический максимум), используя подход итеративного декодирования с мягким решением, при линейной временной сложности с точки зрения длины их блока. Практические реализации в значительной степени полагаются на параллельное декодирование составляющих кодов SPC.

Коды LDPC были впервые введены Робертом Г. Галлагером в его докторской диссертации в 1960 году, но из-за вычислительных усилий при реализации кодера и декодера и введения Рида-Соломона коды, они в основном игнорировались до 1990-х годов.

Коды LDPC теперь используются во многих недавних стандартах высокоскоростной связи, таких как DVB-S2 (цифровое видеовещание — спутниковое — второе поколение), WiMAX ( стандарт IEEE 802.16e для микроволновой связи), высокоскоростная беспроводная локальная сеть (IEEE 802.11n ), 10GBase-T Ethernet (802.3an) и G.hn/G.9960 (Стандарт ITU-T для организации сетей по линиям электропередач, телефонным линиям и коаксиальному кабелю). Другие коды LDPC стандартизированы для стандартов беспроводной связи в пределах 3GPP MBMS (см. исходные коды ).

Турбокоды

Турбокодирование — это схема повторяющегося мягкого декодирования, которая объединяет два или более относительно простых сверточных кода и перемежитель для создания блочного кода, который может работать с точностью до долей децибела. предела Шеннона. Предшествующие LDPC-коды с точки зрения практического применения, теперь они обеспечивают аналогичную производительность.

Одним из первых коммерческих приложений турбо-кодирования была технология цифровой сотовой связи CDMA2000 1x (TIA IS-2000), разработанная Qualcomm и продаваемая Verizon Беспроводная связь, Sprint и другие операторы связи. Он также используется для развития CDMA2000 1x специально для доступа в Интернет, 1xEV-DO (TIA IS-856). Как и 1x, EV-DO был разработан Qualcomm и продается Verizon Wireless, Sprint и другими операторами (маркетинговое название Verizon для 1xEV-DO — Широкополосный доступ, потребительские и бизнес-маркетинговые названия компании Sprint для 1xEV-DO — Power Vision и Mobile Broadband соответственно).

Локальное декодирование и тестирование кодов

Иногда необходимо декодировать только отдельные биты сообщения или проверить, является ли данный сигнал кодовым словом, и делать это, не глядя на все сигнал. Это может иметь смысл в настройке потоковой передачи, где кодовые слова слишком велики для того, чтобы их можно было классически декодировать достаточно быстро, и где на данный момент интересны только несколько битов сообщения. Также такие коды стали важным инструментом в теории сложности вычислений, например, для разработки вероятностно проверяемых доказательств.

Локально декодируемые коды являются кодами с исправлением ошибок, для которых отдельные биты сообщение может быть восстановлено вероятностно, если посмотреть только на небольшое (скажем, постоянное) количество позиций кодового слова, даже после того, как кодовое слово было искажено на некоторой постоянной доле позиций. Локально тестируемые коды — это коды с исправлением ошибок, для которых можно вероятностно проверить, близок ли сигнал к кодовому слову, посмотрев только на небольшое количество позиций сигнала.

Чередование

Чередование часто используется в системах цифровой связи и хранения для повышения производительности кодов прямого исправления ошибок. Многие каналы связи не лишены памяти: ошибки обычно возникают в пакетах, а не независимо друг от друга. Если количество ошибок в кодовом слове превышает возможности кода исправления ошибок, ему не удается восстановить исходное кодовое слово. Чередование облегчает эту проблему путем перетасовки исходных символов по нескольким кодовым словам, тем самым создавая более равномерное распределение ошибок. Поэтому перемежение широко используется для пакетной коррекции ошибок.

. Анализ современных повторяющихся кодов, таких как турбокоды и коды LDPC, обычно предполагает независимое распределение ошибок.. Поэтому системы, использующие коды LDPC, обычно используют дополнительное перемежение символов в кодовом слове.

Для турбокодов перемежитель является неотъемлемым компонентом, и его правильная конструкция имеет решающее значение для хорошей производительности. Алгоритм итеративного декодирования работает лучше всего, когда нет коротких циклов в графе коэффициентов, который представляет декодер; перемежитель выбран, чтобы избежать коротких циклов.

Конструкции перемежителя включают:

- прямоугольные (или однородные) перемежители (аналогично методу с использованием коэффициентов пропуска, описанному выше)

- сверточные перемежители

- случайные перемежители (где перемежитель — известная случайная перестановка)

- S-случайный перемежитель (где перемежитель — это известная случайная перестановка с ограничением, что никакие входные символы на расстоянии S не появляются на расстоянии S на выходе).

- бесконфликтный квадратичный многочлен с перестановками (QPP). Пример использования — в стандарте мобильной связи 3GPP Long Term Evolution.

В системах связи с несколькими несущими может использоваться перемежение по несущим для обеспечения частотного разнесения., например, для уменьшения частотно-избирательного замирания или узкополосных помех.

Пример

Передача без перемежения :

Сообщение без ошибок: aaaabbbbccccddddeeeeffffgggg Передача с пакетной ошибкой: aaaabbbbccc____deeeeffffgggg

Здесь каждая группа одинаковых букв представляет 4-битное однобитовое кодовое слово с исправлением ошибок. Кодовое слово cccc изменяется в один бит и может быть исправлено, но кодовое слово dddd изменяется в трех битах, поэтому либо оно не может быть декодировано вообще, либо может быть декодировано неправильно.

С чередованием :

Ошибка- свободные кодовые слова: aaaabbbbccccddddeeeeffffgggg Interleaved: abcdefgabcdefgabcdefgabcdefg Передача с ошибкой пакета: abcdefgabcd____bcdefgabcdefg Полученные кодовые слова после деинтерлейвинга: "aa_abbb_gg2ccd_dd>,", ",", ",", ","Передача без чередования :

Исходное переданное предложение: ThisIsAnExampleOfInterleaving Полученное предложение с пакетной ошибкой: ThisIs______pleOfInterleavingТермин «AnExample» оказывается в основном неразборчивым и трудным для исправления.

С чередованием :

Переданное предложение: ThisIsAnExampleOfInterleaving... Безошибочная передача: TIEpfeaghsxlIrv.iAaenli.snmOten. Получено предложение с пакетной ошибкой: TIEpfe ______ Irv.iAaenli.snmOten. Полученное предложение после деинтерлейвинга: T_isI_AnE_amp_eOfInterle_vin _...Ни одно слово не потеряно полностью, а недостающие буквы можно восстановить с минимальными догадками.

Недостатки чередования

Использование методов чередования увеличивает общую задержку. Это связано с тем, что весь чередующийся блок должен быть принят до того, как пакеты могут быть декодированы. Также перемежители скрывают структуру ошибок; Без перемежителя более совершенные алгоритмы декодирования могут использовать структуру ошибок и обеспечивать более надежную связь, чем более простой декодер, объединенный с перемежителем. Пример такого алгоритма основан на структурах нейронной сети .

Программное обеспечение для кодов с исправлением ошибок

Моделирование поведения кодов с исправлением ошибок (ECC) в программном обеспечении является обычной практикой для разработки, проверки и улучшения кодов ECC. Предстоящий стандарт беспроводной связи 5G поднимает новый диапазон приложений для программных ECC: Облачные сети радиодоступа (C-RAN) в контексте Программно-определяемого радио (SDR). Идея состоит в том, чтобы напрямую использовать программные ECC в коммуникациях. Например, в 5G программные ECC могут быть расположены в облаке, а антенны могут быть подключены к этим вычислительным ресурсам: таким образом повышается гибкость сети связи и, в конечном итоге, повышается энергоэффективность системы.

В этом контексте существует различное доступное программное обеспечение с открытым исходным кодом, перечисленное ниже (не является исчерпывающим).

- AFF3CT (Панель инструментов быстрого исправления ошибок): полная цепочка связи на C ++ (многие поддерживаемые коды, такие как Turbo, LDPC, полярные коды и т. Д.), Очень быстрая и специализированная на канальном кодировании (может использоваться как программа для моделирования или как библиотека для SDR).

- IT ++ : библиотека классов и функций C ++ для линейной алгебры, числовой оптимизации, обработки сигналов, связи и статистики.

- OpenAir : реализация (на языке C) спецификаций 3GPP, касающихся Evolved Packet Core Networks.

Список кодов исправления ошибок

| Расстояние | Код |

|---|---|

| 2 (обнаружение единичной ошибки) | Четность |

| 3 (исправление одиночной ошибки) | Тройное модульное резервирование |

| 3 (исправление одиночной ошибки) | совершенное Хэмминга, такое как Хэмминга (7,4) |

| 4 (SECDED ) | Расширенный Хэмминга |

| 5 (исправление двойной ошибки) | |

| 6 (исправление двойной ошибки / обнаружение тройной ошибки) | |

| 7 (исправление трех ошибок) | совершенный двоичный код Голея |

| 8 (TECFED) | расширенный двоичный код Голея |

- коды AN

- код BCH, который может быть разработан для исправления любого произвольного количества ошибок в кодовом блоке.

- код Бергера

- код постоянного веса

- сверточный код

- Расширительные коды

- Групповые коды

- коды Голея, из которых двоичный код Голея представляет практический интерес

- код Гоппа, используемый в Криптосистема Мак-Элиса

- Код Адамара

- Код Хагельбаргера

- Код Хэмминга

- Код на основе латинского квадрата для небелого шума (преобладающий, например, в широкополосной связи по сравнению с линиями электропередач)

- Лексикографический код

- Линейное сетевое кодирование, тип кода с исправлением стирания в сетях вместо двухточечных ссылок

- Длинный код

- Код проверки четности с низкой плотностью, также известный как код Галлагера, как архетип для кодов разреженного графа

- LT-кода, который является почти оптимальным бесскоростным кодом коррекции стирания (код Фонтана)

- m из n кодов

- Онлайн-код, почти оптимальный код бесскоростной коррекции стирания

- Полярный код (codi ng теория)

- Код Raptor, почти оптимальный код с бесскоростной коррекцией стирания

- Исправление ошибок Рида – Соломона

- Код Рида – Маллера

- Код повторения-накопления

- Коды повторения, например, Тройная модульная избыточность

- Спинальный код, бесскоростной нелинейный код, основанный на псевдослучайных хэш-функциях

- Код Торнадо, почти оптимальный код коррекции стирания, и предшественник кодов Фонтана

- Турбо-код

- код Уолша – Адамара

- Циклические проверки избыточности (CRC) могут исправлять 1-битные ошибки для сообщений не более 2 n - 1 - 1 { displaystyle 2 ^ {n-1} -1}

бит длиной для оптимальных порождающих полиномов степени n { displaystyle n}

, см. Математика циклических проверок избыточности # Битовые фильтры

См. Также

- Скорость кода

- Коды стирания

- Декодер с мягким решением

- Пакетный код исправления ошибок

- Обнаружение и исправление ошибок

- Ошибка -корректирующие коды с обратной связью

Ссылки

Дополнительная литература

- Clark, Jr., George C.; Каин, Дж. Бибб (1981). Кодирование с коррекцией ошибок для цифровой связи. Нью-Йорк, США: Plenum Press. ISBN 0-306-40615-2. ISBN 978-0-306-40615-7.

- Уикер, Стивен Б. (1995). Системы контроля ошибок для цифровой связи и хранения. Энглвуд Клиффс, Нью-Джерси, США: Прентис-Холл. ISBN 0-13-200809-2. ISBN 978-0-13-200809-9.

- Уилсон, Стивен Г. (1996). Цифровая модуляция и кодирование. Энглвуд Клиффс, Нью-Джерси, США: Прентис-Холл. ISBN 0-13-210071-1. ISBN 978-0-13-210071-7.

- "Код коррекции ошибок в одноуровневой ячейке NAND флэш-памяти « 16 февраля 2007 г.

- « Код исправления ошибок во флэш-памяти NAND » 29 ноября 2004 г.

- Наблюдения за ошибками, исправлениями и доверием зависимых систем, Джеймс Гамильтон, 26 февраля 2012 г.

- Сферические упаковки, решетки и группы, Дж. Х. Конвей, NJA Sloane, Springer Science Business Media, 9 марта 2013 г. - Математика - 682 страницы.

Внешние ссылки

- Морелос -Зарагоса, Роберт (2004). "Страница корректирующих кодов (ECC)". Проверено 5 марта 2006 г.

- lpdec: библиотека для декодирования LP и связанных вещей (Python)

бит длиной для оптимальных порождающих полиномов степени n { displaystyle n}

бит длиной для оптимальных порождающих полиномов степени n { displaystyle n} , см. Математика циклических проверок избыточности # Битовые фильтры

, см. Математика циклических проверок избыточности # Битовые фильтры