Working with 2014 version of Quartus II software (web edition), I receive the error 10170 when compiling the following code:

module shifter16 (A, H_sel, H)

input [15:0]A;

input H_sel;

output [15:0]H;

reg [15:0] H;

always @ (A or H_sel)

begin

if (H_sel)

H={A[14:0],1'b0};

else

H={A[15],A[15:1]};

end

endmodule

Error received:

Error (10170): Verilog HDL syntax error at shifter16.v(2) near text «input»; expecting «;»

Qiu

5,54110 gold badges49 silver badges56 bronze badges

asked Apr 22, 2014 at 17:26

You need a semicolon at the end of the first line:

module shifter16 (A, H_sel, H);

answered Apr 22, 2014 at 17:39

AriAri

7,07110 gold badges38 silver badges66 bronze badges

0

The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000075173

Content Type: Error Messages

Last Reviewed: 11/24/2014

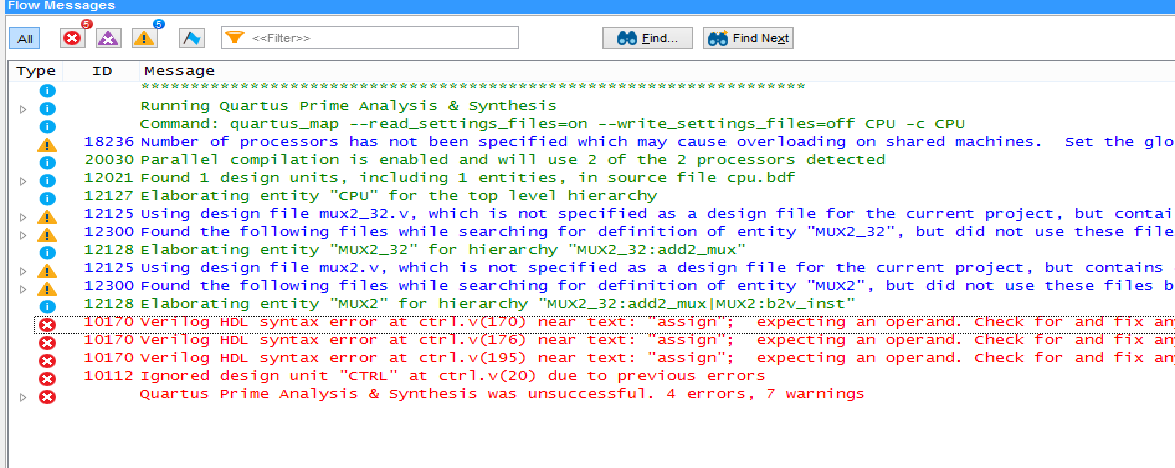

Error (10170): Verilog HDL syntax error at <Verilog_file>.v(line_number) near text «,»; expecting an operand

Environment

Version Found: 13.1

Due to a problem in the Quartus® II software version 13.1 and later, you may get the following error when compiling a Verilog HDL file that has converted from a Block Design File (.bdf).

The cause of the error is due to the generated Verilog HDL file has a extra comma in the port connections.

To workaround the error, manually delete the extra comma in the <Verilog_file>.v(line_number).

This problem is schedule to be fixed in future release of the Quartus II software.

- Description

- Resolution

Need more help?

Give Feedback

Disclaimer

The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000074408

Content Type: Error Messages

Last Reviewed: 06/18/2007

Error (10170): Verilog HDL syntax error at <location> near text «generate»; expecting «end», or an identifier («generate» is a reserved keyword ), or a sequential statement

Environment

You may get this error if your design uses extra generate/endgenerate statements for nested loops. Older versions of the Quartus® II software erroneously accepted nested generate/endgenerate statements in Verilog HDL design files. The Quartus II software beginning with version 6.0 correctly flags nested generate/endgenerate statements as an error.

If you have loops within a loop, you only need one generate/endgenerate pair, as shown in the following example that reverses the bits in a bus.

genvar i,j;

generate

for( i=0; i<8; i=i 1 )

begin : outer

for (j=0; j<8; j=j 1 )

begin : inner

assign data_out[i][j] = data_in[7-i][7-j];

end

end

endgenerate

- Description

Need more help?

Give Feedback

Disclaimer

За последние несколько событий некоторые из наших читателей сообщили нам, где они столкнулись с синтаксической ошибкой 10170 Verilog липопротеина высокой плотности./ Ошибка (10170): синтаксическая ошибка Verilog HDL на всем протяжении .v (номер_строки) рядом с текстовым сообщением “,”; желает операнд. Из-за вашей проблемы с программным обеспечением Quartus® II типа 13.1 и выше, вы также можете получить следующую ошибку при компиляции файла Verilog HDL, преобразованного из файла данных блочного дизайна (.bdf).

Но если вы определенно не используете System Verilog (и ваше старомодное кодирование предполагает, что клиенты этого не делают), вы обнаружите, что все

на самом деле не компилируется, потому что целью nominate должен быть wire , а не большинство недавний reg . И если вы переключите product на обычный перенос , вы обнаружите, что эти сделки дают вам ошибку:

потому что последний человек не может сопоставить thread в новом большом блоке always (или действительно ).

Кажется, вы всегда разрабатываете большинство видов смещения и добавляете множитель и / или вы, вероятно, хотите инициализировать тип product в начале, как при вычислении. (Предполагая, что вы группируете синтаксис) телефонные линии

непрерывная и непрерывная реклама связана с продуктом ; они фактически не инициализируют product . Здесь вы создаете персональные компьютеры, а не пишете программное обеспечение.

123-й4-й56-е7-е8-едевять10одиннадцать12-е1314-епятнадцать1617-е18-е19-е20-е21 год22-е23242526 год2728 год2930-е31 год32333435 лет363738394041 год4243 года44 год45464748495051525354555657 лет5859

модуль kj (j1, l1, j, k, timepiece, reset, q, qb, q1, qb1, b);Вход j1, l1, j, k, часы, сброс;Выходной reg q1, qb1;Рег уйти. [3: 0] q, qb, b, a;всегда в (отрицательные часы)начинатьСлучай (сброс, j1, l1)3'b100: q1 = q1;3'b101: q1 равно 0;3'b110: q1 = 1;3'b111: q1 =! q1;По умолчанию: q1 = 0;Задняя обложкаqb1 <=! q1;конецвсегда@ *начинатьесли (q1 == q1)начинатьkl JK1 (j, k, рабочее время, сброс, q [0], qb [0]);kl JK2 (j, nited Kingdom, q [0], reset, q [1], qb [1]);kl JK3 (j, k, q [1], сброс, q [2], защитник [2]);kl JK4 (j, k, q [2], сбросить, e [3], qb [3]);конецконецв противном случае, если (q1 == 0)начинатьkl JK5 (j, k, d, сброс, q [0], защитник [0]);kl JK6 (j, k, q [0], сброс, королева [1], qb [1]);kl JK7 (j, k, q [1], сбросить в ноль, q [2], qb [2]);kl JK8 (j, k, b [2], сбросить, q [3], qb [3]);конецАв противном случае, будет ли (q1 == 1)начинатьвсегда @ (сбросить)начинатьесли (сбросить)q <= 4'b0000;в противном случае, если возможно (q <4'b0101)d <= d + 1;Другаяб = ш [1] && q [3];конецконецАиначе каждый раз часы)начинатьесли (сбросить)q (q1 == ~ q1)начинатьвсегда @ (Posege <= 4'b0000;в противном случае в пределах (q <4'b0011)d <= d + 1;Другаяa равно d [2] и d [3];конецконецФинальный модуль

Зачем нужно вводить CAPTCHA?

Заполнение CAPTCHA доказывает, что вы 1 важный человек, и дает вам временный доступ в Интернет.

Что я могу сделать, чтобы этого избежать в будущем?

Если у вашего сайта есть надежное соединение, например, в собственности, вы можете запустить сканирование на вирусы на всем своем устройстве, чтобы убедиться, что оно не заражено вредоносным ПО.

Если вы находитесь в офисе или в большой группе, вы можете попросить своего сетевого администратора, а также запустить сканирование сети, чтобы найти неправильно настроенные или возможно зараженные устройства.

Еще один способ предотвратить доступ к этой странице в будущем — это, скорее всего, использование Privacy Pass. Вы действительно запрашиваете загрузку версии 2.0 из Магазина надстроек Firefox прямо сейчас.

Ошибка 10170 Синтаксическая ошибка при компиляции

Я действительно новичок в Verilog. Имеется заслуживающая доверия соответствующая ошибка компиляции для оператора if.

Может ли кто-нибудь помочь мне, указав на самую большую ошибку?

Это часть кода, который я написал. Да (10170): сохранение с ошибками

Синтаксическая ошибка Verilog HDL из-за seqdet.v (24) рядом с текстом «если»;

Ожидание идентификатора («if» определенно является запланированным ключевым словом) или числа любого типа, системной цели или «(«, плюс «{» или унарного оператора,

current_state — это своего рода регистр, но reset_state инициализируется значением 3’b000, что позволяет использовать нашу собственную инструкцию параметра.

Опубликовать во времена Джагхеда

Я новичок в Verilog. Системная ошибка оператора if.

Может ли кто-нибудь поддержать меня, указав на серьезныеЕсть ли ошибка? [2: 0]

reg next_state, current_state;

выдает reset_state = 3’b000;

case (данные)

{

предположение (current_state == reset_state)

начало

next_state = reset_state;

конец

Это последняя часть кода, который я написал. Следующие

ошибки (10170): синтаксическая ошибка Verilog HDL в seqdet.v (24) далее в отношении слов «if»;

ожидает идентификатор («if», без сомнения, зарезервированное поисковое выражение), или невероятное число, системная задача, или «(«, или, может быть, «{«, или унарный оператор,

current_state может предоставить регистр типа, а вставки reset_state недавно были инициализированы до 3’b000 с использованием параметраounter.

Спасибо,

Aravind

Выше я узнал, что в кейсе еще не было инструкций о том, как начать процесс, а также о том, как его завершить

и обычно, и у них были круглые скобки, которые, на мой взгляд, действительно были необходимы. Я не уверен, прав ли я, но, к сожалению, сейчас я не получаю сообщение об ошибке.

Расположены используется для битовой строки. Фактически используйте start-end.

Не забывайте о «заглушке».

Расположены используется для битовой строки. Вместо этого используйте start-end.

Не забывайте, однако, «endcase».

г.

Recommended

Speed up your PC today with this easy-to-use download.

You may encounter an error indicating syntax error 10170 verilog hdl. It turns out that there are several ways to solve this problem, and this is what we will now look at. / Error (10170): Verilog HDL syntax error in .v (line_number) next to text message “,”; expects an operand. Due to your issue with Quartus® II software type 13.1 and above, you may receive the following error when compiling a Verilog HDL file converted from a block design file (.bdf).

Due to the situation in Quartus® II software version 13.1 and shortly thereafter, you may receive the following error message when Verilog compiles an HDL file converted from an HDL file: block construction (.bdf).

The reason for the error is that the entire generated Verilog HDL file contains almost all the extra commas in mov connections.

The reason for your syntax error can be described in such a way that you cannot simply write:

Product [7: 4] matches 4'b0000;

assign product [7: 4] is 4'b0000;

But if you are not using System Verilog (and your old-fashioned coding style might suggest that you are not), you will find that

product assignment [7: 4] includes 4'b0000;

also doesn’t compile, because the sad victim of the assign statement should automatically be wire , not reg . And if you replace product with a new stream , you will find yourself getting instructions and errors like this:

product means product >> 1; // move well and set the high bit to 0Product [7: 3] = product denion [7: 3] + multiplicable [4: 0]; // add 5 bits, so we'll probably deal with carry

product = fabric >> 1; // move all the way to the right

because you cannot assign a full stream in a always (or initial ) block.

You are starting to design a “shift and add art” multiplier and you probably really want to initialize the product at the beginning of the calculation. (Assuming you are creating syntax) lines

(assign) [7: 4] item = 4'b0000;(Assignment) the product [3: 0] is equal to the multiplier [3: 0];

run product constantly, every time; they do not initialize product . This is where you design hardware, not software.

Recommended

Is your PC running slow? Do you have problems starting up Windows? Don’t despair! ASR Pro is the solution for you. This powerful and easy-to-use tool will diagnose and repair your PC, increasing system performance, optimizing memory, and improving security in the process. So don’t wait — download ASR Pro today!

1234th56th7th8thnineteneleven12th13th14thfifteen1617th18th19th20th21 years22nd232425262728 year2930th31 year32333435 year363738394041 years4243 years old44 years45464748495051525354555657 years old5859

module kj (j1, l1, j, k, clock, reset, q, qb, q1, qb1, b);Input j1, l1, j, k, clock, reset;Output reg q1, qb1;Reg exit. [3: 0] q, qb, b, a;always @ (negative hours)beginCase (reset, j1, l1)3'b100: q1 = q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 = ~ q1;Default : q1 = 0;Back coverqb1 <= ~ q1;[email protected] *beginif (q1 == q1)beginkl JK1 (j, k, hours, reset, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], qb [1]);kl JK3 (j, k, q [1], reset, q [2], qb [2]);kl JK4 (j, k, q [2], reset, q [3], qb [3]);endendotherwise, if (q1 == 0)beginkl JK5 (j, k, d, reset, q [0], qb [0]);kl JK6 (j, k, q [0], reset, q [1], qb [1]);kl JK7 (j, k, q [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], qb [3]);endAotherwise, if (q1 == 1)beginalways @ (reset)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0101)d <= d + 1;anotherb = q [1] && q [3];endendAotherwise, if (q1 == ~ q1)beginalways @ (clock setting)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0011)qQ + 1;AnotherA = q [2] & q [3];endendFinal module

<=

Why Do I Need To Fill In The CAPTCHA?

Completing this CAPTCHA proves that you are human and gives you temporary access to a web resource.

What Can I Do To Prevent This From Happening In The Future?

If you are more likely to have face-to-face communication, such as visiting your home, you can run a scancheck for viruses on your device to make sure it is not infected with malware.

If you are in the office or on a shared network, you can find a network administrator who will run a custom network scan to support misconfigured or infected devices.

Another way to reduce access to this page in the enhanced version is to use Passport Privacy. You may now need to download version 2.0 from the Firefox Add-on Store.

Error 10170 Compilation format error

I am the latest in Verilog. System error of the if statement.

Can a person help me by rejecting my mistake?

This is partially related code I wrote. The following

error occurs

Error (10170): Verilog HDL syntax error in seqdet.v (24) next to if content;

Waiting for an identifier («if» is a reserved keyword), quantity, system or

backchi, or «(» and also «{» or unary operator,

current_state is in register type, and reset_state was initialized to 3’b000 using the

parameter instruction.

Post by Jughead

I’m new to Verilog. Collect error for if statement.

Can the player help me by pointing out my mistake ?. [2: 0]

reg next_state, current_state;

the reset_state parameter means 3’b000;

case (data)

{

if (current_state == reset_state)

begin

next_state means reset_state;

end

This is part because of the code I wrote. There is the following error

Verilog error (10170): HDL syntax error in seqdet.v (24) next to the anchor text «if»;

Waiting for an identifier («if» is a keyword of any type of reserved identifier), or #, or

of a system task, or «(«, with «{«, or a unary operator,

current_state is associated with a type register, and reset_state is initialized to 3 ‘b000 with parameter declaration. Out

thanks,

aravind

This case statement did not have large opening and closing

statements, and it was enclosed in curly braces, which, in my opinion, was unnecessary. Not sure if I’m right. But now I am notI understand all our mistakes.

used for bitstring. Use start-end instead.

Don’t forget the «endcase».

used for both bitstring. Use start-end instead. Film Not such an «extreme case».

Speed up your PC today with this easy-to-use download.

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl

Содержание

- Error 10170 Verilog HDL Syntax Error? Repair Immediately

- Recommended

- Recommended

- What Can I Do To Prevent This From Happening In The Future?

Error 10170 Verilog HDL Syntax Error? Repair Immediately

Table of Contents

Recommended

You may encounter an error indicating syntax error 10170 verilog hdl. It turns out that there are several ways to solve this problem, and this is what we will now look at. / Error (10170): Verilog HDL syntax error in .v (line_number) next to text message “,”; expects an operand. Due to your issue with Quartus® II software type 13.1 and above, you may receive the following error when compiling a Verilog HDL file converted from a block design file (.bdf).

Due to the situation in Quartus® II software version 13.1 and shortly thereafter, you may receive the following error message when Verilog compiles an HDL file converted from an HDL file: block construction (.bdf).

The reason for the error is that the entire generated Verilog HDL file contains almost all the extra commas in mov connections.

The reason for your syntax error can be described in such a way that you cannot simply write:

But if you are not using System Verilog (and your old-fashioned coding style might suggest that you are not), you will find that

also doesn’t compile, because the sad victim of the assign statement should automatically be wire , not reg . And if you replace product with a new stream , you will find yourself getting instructions and errors like this:

because you cannot assign a full stream in a always (or initial ) block.

You are starting to design a “shift and add art” multiplier and you probably really want to initialize the product at the beginning of the calculation. (Assuming you are creating syntax) lines

run product constantly, every time; they do not initialize product . This is where you design hardware, not software.

Recommended

Is your PC running slow? Do you have problems starting up Windows? Don’t despair! ASR Pro is the solution for you. This powerful and easy-to-use tool will diagnose and repair your PC, increasing system performance, optimizing memory, and improving security in the process. So don’t wait — download ASR Pro today!

Why Do I Need To Fill In The CAPTCHA?

Completing this CAPTCHA proves that you are human and gives you temporary access to a web resource.

What Can I Do To Prevent This From Happening In The Future?

If you are more likely to have face-to-face communication, such as visiting your home, you can run a scancheck for viruses on your device to make sure it is not infected with malware.

If you are in the office or on a shared network, you can find a network administrator who will run a custom network scan to support misconfigured or infected devices.

Another way to reduce access to this page in the enhanced version is to use Passport Privacy. You may now need to download version 2.0 from the Firefox Add-on Store.

Error 10170 Compilation format error

I am the latest in Verilog. System error of the if statement.

Can a person help me by rejecting my mistake?

This is partially related code I wrote. The following

error occurs

Error (10170): Verilog HDL syntax error in seqdet.v (24) next to if content;

Waiting for an identifier («if» is a reserved keyword), quantity, system or

backchi, or «(» and also «<» or unary operator,

current_state is in register type, and reset_state was initialized to 3’b000 using the

parameter instruction.

Post by Jughead

I’m new to Verilog. Collect error for if statement.

Can the player help me by pointing out my mistake ?. [2: 0]

reg next_state, current_state;

the reset_state parameter means 3’b000;

case (data)

<

if (current_state == reset_state)

begin

next_state means reset_state;

end

This is part because of the code I wrote. There is the following error

Verilog error (10170): HDL syntax error in seqdet.v (24) next to the anchor text «if»;

Waiting for an identifier («if» is a keyword of any type of reserved identifier), or #, or

of a system task, or «(«, with » <«, or a unary operator,

current_state is associated with a type register, and reset_state is initialized to 3 ‘b000 with parameter declaration. Out

thanks,

aravind

This case statement did not have large opening and closing

statements, and it was enclosed in curly braces, which, in my opinion, was unnecessary. Not sure if I’m right. But now I am notI understand all our mistakes.

used for bitstring. Use start-end instead.

Don’t forget the «endcase».

used for both bitstring. Use start-end instead. Film Not such an «extreme case».

Источник

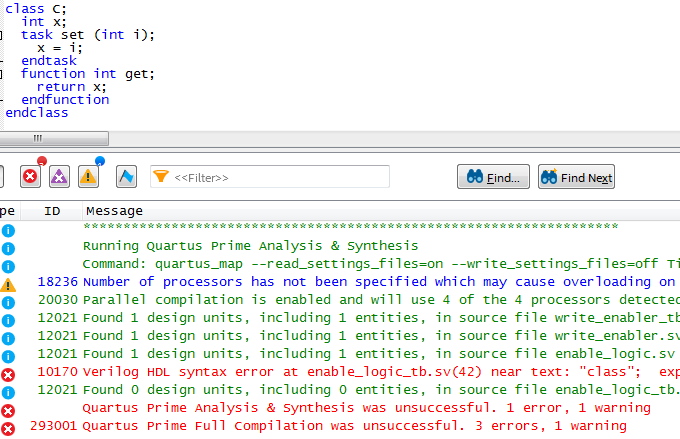

Пример-копипаста из книги:

module test2(input logic [3:0] a, input logic en, output tri [3:0] y);

assign y = en ? a : 4’bz;

endmodule

Ошибки:

Error (10170): Verilog HDL syntax error at test2.v(2) near text

Error (10170): Verilog HDL syntax error at test2.v(2) near text «»; expecting «;»

Error (10112): Ignored design unit «test2» at test2.v(1) due to previous errors

WTF?

-

Вопрос заданболее трёх лет назад

-

1392 просмотра

Пригласить эксперта

По умолчанию во многих CAE синтез верилога идёт подразумевая настройку синтаксиса verilog-95,

вам следует изменить настройки (по описанию портов видно, что это минимум verilog-2001, а по резервированному слову logic — SV)

-

Показать ещё

Загружается…

09 февр. 2023, в 13:58

2000 руб./за проект

09 февр. 2023, в 13:28

777 руб./за проект

09 февр. 2023, в 13:09

5000 руб./за проект