Working with 2014 version of Quartus II software (web edition), I receive the error 10170 when compiling the following code:

module shifter16 (A, H_sel, H)

input [15:0]A;

input H_sel;

output [15:0]H;

reg [15:0] H;

always @ (A or H_sel)

begin

if (H_sel)

H={A[14:0],1'b0};

else

H={A[15],A[15:1]};

end

endmodule

Error received:

Error (10170): Verilog HDL syntax error at shifter16.v(2) near text «input»; expecting «;»

Qiu

5,54110 gold badges49 silver badges56 bronze badges

asked Apr 22, 2014 at 17:26

You need a semicolon at the end of the first line:

module shifter16 (A, H_sel, H);

answered Apr 22, 2014 at 17:39

AriAri

7,07110 gold badges38 silver badges66 bronze badges

0

The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000075173

Content Type: Error Messages

Last Reviewed: 11/24/2014

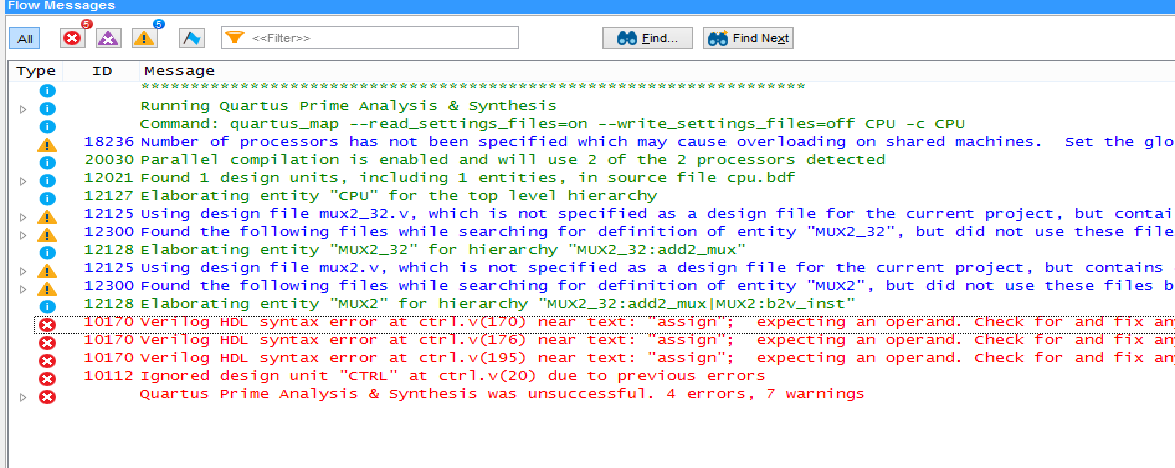

Error (10170): Verilog HDL syntax error at <Verilog_file>.v(line_number) near text «,»; expecting an operand

Environment

Version Found: 13.1

Due to a problem in the Quartus® II software version 13.1 and later, you may get the following error when compiling a Verilog HDL file that has converted from a Block Design File (.bdf).

The cause of the error is due to the generated Verilog HDL file has a extra comma in the port connections.

To workaround the error, manually delete the extra comma in the <Verilog_file>.v(line_number).

This problem is schedule to be fixed in future release of the Quartus II software.

- Description

- Resolution

Need more help?

Give Feedback

Disclaimer

The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000074408

Content Type: Error Messages

Last Reviewed: 06/18/2007

Error (10170): Verilog HDL syntax error at <location> near text «generate»; expecting «end», or an identifier («generate» is a reserved keyword ), or a sequential statement

Environment

You may get this error if your design uses extra generate/endgenerate statements for nested loops. Older versions of the Quartus® II software erroneously accepted nested generate/endgenerate statements in Verilog HDL design files. The Quartus II software beginning with version 6.0 correctly flags nested generate/endgenerate statements as an error.

If you have loops within a loop, you only need one generate/endgenerate pair, as shown in the following example that reverses the bits in a bus.

genvar i,j;

generate

for( i=0; i<8; i=i 1 )

begin : outer

for (j=0; j<8; j=j 1 )

begin : inner

assign data_out[i][j] = data_in[7-i][7-j];

end

end

endgenerate

- Description

Need more help?

Give Feedback

Disclaimer

Recommended

Speed up your PC today with this easy-to-use download.

You may encounter an error indicating syntax error 10170 verilog hdl. It turns out that there are several ways to solve this problem, and this is what we will now look at. / Error (10170): Verilog HDL syntax error in .v (line_number) next to text message “,”; expects an operand. Due to your issue with Quartus® II software type 13.1 and above, you may receive the following error when compiling a Verilog HDL file converted from a block design file (.bdf).

Due to the situation in Quartus® II software version 13.1 and shortly thereafter, you may receive the following error message when Verilog compiles an HDL file converted from an HDL file: block construction (.bdf).

The reason for the error is that the entire generated Verilog HDL file contains almost all the extra commas in mov connections.

The reason for your syntax error can be described in such a way that you cannot simply write:

Product [7: 4] matches 4'b0000;

assign product [7: 4] is 4'b0000;

But if you are not using System Verilog (and your old-fashioned coding style might suggest that you are not), you will find that

product assignment [7: 4] includes 4'b0000;

also doesn’t compile, because the sad victim of the assign statement should automatically be wire , not reg . And if you replace product with a new stream , you will find yourself getting instructions and errors like this:

product means product >> 1; // move well and set the high bit to 0Product [7: 3] = product denion [7: 3] + multiplicable [4: 0]; // add 5 bits, so we'll probably deal with carry

product = fabric >> 1; // move all the way to the right

because you cannot assign a full stream in a always (or initial ) block.

You are starting to design a “shift and add art” multiplier and you probably really want to initialize the product at the beginning of the calculation. (Assuming you are creating syntax) lines

(assign) [7: 4] item = 4'b0000;(Assignment) the product [3: 0] is equal to the multiplier [3: 0];

run product constantly, every time; they do not initialize product . This is where you design hardware, not software.

Recommended

Is your PC running slow? Do you have problems starting up Windows? Don’t despair! ASR Pro is the solution for you. This powerful and easy-to-use tool will diagnose and repair your PC, increasing system performance, optimizing memory, and improving security in the process. So don’t wait — download ASR Pro today!

1234th56th7th8thnineteneleven12th13th14thfifteen1617th18th19th20th21 years22nd232425262728 year2930th31 year32333435 year363738394041 years4243 years old44 years45464748495051525354555657 years old5859

module kj (j1, l1, j, k, clock, reset, q, qb, q1, qb1, b);Input j1, l1, j, k, clock, reset;Output reg q1, qb1;Reg exit. [3: 0] q, qb, b, a;always @ (negative hours)beginCase (reset, j1, l1)3'b100: q1 = q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 = ~ q1;Default : q1 = 0;Back coverqb1 <= ~ q1;[email protected] *beginif (q1 == q1)beginkl JK1 (j, k, hours, reset, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], qb [1]);kl JK3 (j, k, q [1], reset, q [2], qb [2]);kl JK4 (j, k, q [2], reset, q [3], qb [3]);endendotherwise, if (q1 == 0)beginkl JK5 (j, k, d, reset, q [0], qb [0]);kl JK6 (j, k, q [0], reset, q [1], qb [1]);kl JK7 (j, k, q [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], qb [3]);endAotherwise, if (q1 == 1)beginalways @ (reset)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0101)d <= d + 1;anotherb = q [1] && q [3];endendAotherwise, if (q1 == ~ q1)beginalways @ (clock setting)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0011)qQ + 1;AnotherA = q [2] & q [3];endendFinal module

<=

Why Do I Need To Fill In The CAPTCHA?

Completing this CAPTCHA proves that you are human and gives you temporary access to a web resource.

What Can I Do To Prevent This From Happening In The Future?

If you are more likely to have face-to-face communication, such as visiting your home, you can run a scancheck for viruses on your device to make sure it is not infected with malware.

If you are in the office or on a shared network, you can find a network administrator who will run a custom network scan to support misconfigured or infected devices.

Another way to reduce access to this page in the enhanced version is to use Passport Privacy. You may now need to download version 2.0 from the Firefox Add-on Store.

Error 10170 Compilation format error

I am the latest in Verilog. System error of the if statement.

Can a person help me by rejecting my mistake?

This is partially related code I wrote. The following

error occurs

Error (10170): Verilog HDL syntax error in seqdet.v (24) next to if content;

Waiting for an identifier («if» is a reserved keyword), quantity, system or

backchi, or «(» and also «{» or unary operator,

current_state is in register type, and reset_state was initialized to 3’b000 using the

parameter instruction.

Post by Jughead

I’m new to Verilog. Collect error for if statement.

Can the player help me by pointing out my mistake ?. [2: 0]

reg next_state, current_state;

the reset_state parameter means 3’b000;

case (data)

{

if (current_state == reset_state)

begin

next_state means reset_state;

end

This is part because of the code I wrote. There is the following error

Verilog error (10170): HDL syntax error in seqdet.v (24) next to the anchor text «if»;

Waiting for an identifier («if» is a keyword of any type of reserved identifier), or #, or

of a system task, or «(«, with «{«, or a unary operator,

current_state is associated with a type register, and reset_state is initialized to 3 ‘b000 with parameter declaration. Out

thanks,

aravind

This case statement did not have large opening and closing

statements, and it was enclosed in curly braces, which, in my opinion, was unnecessary. Not sure if I’m right. But now I am notI understand all our mistakes.

used for bitstring. Use start-end instead.

Don’t forget the «endcase».

used for both bitstring. Use start-end instead. Film Not such an «extreme case».

Speed up your PC today with this easy-to-use download.

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl

Пример-копипаста из книги:

module test2(input logic [3:0] a, input logic en, output tri [3:0] y);

assign y = en ? a : 4’bz;

endmodule

Ошибки:

Error (10170): Verilog HDL syntax error at test2.v(2) near text

Error (10170): Verilog HDL syntax error at test2.v(2) near text «»; expecting «;»

Error (10112): Ignored design unit «test2» at test2.v(1) due to previous errors

WTF?

-

Вопрос заданболее трёх лет назад

-

1392 просмотра

Пригласить эксперта

По умолчанию во многих CAE синтез верилога идёт подразумевая настройку синтаксиса verilog-95,

вам следует изменить настройки (по описанию портов видно, что это минимум verilog-2001, а по резервированному слову logic — SV)

-

Показать ещё

Загружается…

09 февр. 2023, в 13:58

2000 руб./за проект

09 февр. 2023, в 13:28

777 руб./за проект

09 февр. 2023, в 13:09

5000 руб./за проект

Минуточку внимания

The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000079408

Content Type: Error Messages

Last Reviewed: 09/11/2012

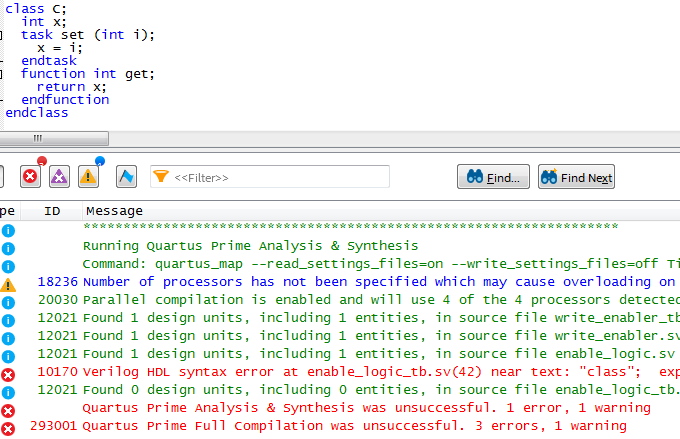

Error (10170): Verilog HDL Syntax Error at <filename> near text «int»; expecting an identifier («int» is a reserved keyword)

Environment

In the Quartus® II software may generate this error when you declare multiple loop variables within a SystemVerilog FOR loop, because this syntax is currently unsupported.

The following is an example of unsupported syntax: for(int i=0, int j=0; i<4, j<2; i , j )

To work around this problem, declare only one loop variable within the FOR loop.

Use the following supported syntax to work around this problem: int j=0;

for(int i=0, j=0; i<4, j<2; i , j )

This problem is scheduled to be fixed in a future release of the Quartus II software.

- Description

Need more help?

Give Feedback

Disclaimer

Skip to main content

Welcome to EDAboard.com

Welcome to our site! EDAboard.com is an international Electronics Discussion Forum focused on EDA software, circuits, schematics, books, theory, papers, asic, pld, 8051, DSP, Network, RF, Analog Design, PCB, Service Manuals… and a whole lot more! To participate you need to register. Registration is free. Click here to register now.

-

Digital Design and Embedded Programming

-

Digital Signal Processing

You should upgrade or use an alternative browser.

Error in Verilog problem

-

Thread starterGaurav Sarode

-

Start dateMay 9, 2012

- Status

- Not open for further replies.

-

#1

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

Code Verilog - [expand]

Last edited by a moderator: May 9, 2012

-

#2

- Joined

- Feb 1, 2011

- Messages

- 115

- Helped

- 4

- Reputation

-

8

- Reaction score

- 4

- Trophy points

- 1,298

- Location

-

Noida

- Activity points

-

2,381

-

#3

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

Thanx for ur rpl

I have made changes that u suggested but still m getting errors, m using Quartus II

the errors are as follows

Error (10170): Verilog HDL syntax error at imp.v(28) near text «gt1»; expecting «<=», or «=»

Error (10170): Verilog HDL syntax error at imp.v(29) near text «gt2»; expecting «<=», or «=»

Error (10170): Verilog HDL syntax error at imp.v(30) near text «gt3»; expecting «<=», or «=»

Error (10170): Verilog HDL syntax error at imp.v(34) near text «(«; expecting «;», or «,»

Error (10149): Verilog HDL Declaration error at imp.v(34): identifier «temp_r» is already declared in the present scope

Error (10170): Verilog HDL syntax error at imp.v(34) near text «)»; expecting «;», or «,»

Error (10170): Verilog HDL syntax error at imp.v(35) near text «(«; expecting «;», or «,»

Error (10149): Verilog HDL Declaration error at imp.v(35): identifier «temp_g» is already declared in the present scope

Error (10170): Verilog HDL syntax error at imp.v(35) near text «)»; expecting «;», or «,»

Error (10170): Verilog HDL syntax error at imp.v(36) near text «(«; expecting «;», or «,»

Error (10149): Verilog HDL Declaration error at imp.v(36): identifier «temp_b» is already declared in the present scope

Error (10170): Verilog HDL syntax error at imp.v(36) near text «)»; expecting «;», or «,»

Error (10170): Verilog HDL syntax error at imp.v(37) near text «(«; expecting «;», or «,»

Error (10149): Verilog HDL Declaration error at imp.v(37): identifier «r1» is already declared in the present scope

Error (10170): Verilog HDL syntax error at imp.v(37) near text «)»; expecting «;», or «,»

Error (10170): Verilog HDL syntax error at imp.v(38) near text «(«; expecting «;», or «,»

Error (10149): Verilog HDL Declaration error at imp.v(38): identifier «r1» is already declared in the present scope

Error (10170): Verilog HDL syntax error at imp.v(38) near text «)»; expecting «;», or «,»

Error (10170): Verilog HDL syntax error at imp.v(49) near text «(«; expecting «;», or «,»

Error: Quartus II Analysis & Synthesis was unsuccessful. 19 errors, 7 warnings

Error: Peak virtual memory: 183 megabytes

Error: Processing ended: Thu May 10 10:45:19 2012

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:02

Error: Quartus II Full Compilation was unsuccessful. 21 errors, 7 warnings

———- Post added at 06:23 ———- Previous post was at 06:17 ———-

I have written code fro ROM where i hve stored image information and have separate code for RAM which is being modified depending on the operation carried out by sgmtnbox i.e. depends on its output decison

-

#4

You are trying to instantiate modules inside an always block. That’s not possible according to Verilog rules. (Neither in VHDL, by the way).

-

#5

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

I want to implement iterative operation on FPGA…and m not getting a way out of it pls help

———- Post added at 08:00 ———- Previous post was at 07:59 ———-

@Fvm

I want to implement iterative operation on FPGA…and m not getting a way out of it pls help

-

#6

A for loop in HDL is not defining a sequence in time rather than parallel logic. Apart from other problems, the iteration construct in your code will generate 485 logic instances, which very likely execeeds any reasonable resource limits.

Module instances have to placed in concurrent code, outside laways blocks. To generate multiple instances in a loop, use a generate construct.

I guess, that th eintended iteration can be implemented as sequential processing, one iteration step per clock cycle. But I don’t understand th eapplication problem in detail.

-

#7

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

I want to perform image segmentation for that i have to compare the pixel color value with all the other pixels color values, so i have saved the pixel color values in ROM and want to get following two tables from it

-

#8

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

In MATLAB it was done with two nested for loops…

-

#9

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

-

#10

-

#11

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

-

#12

- Joined

- Jan 25, 2010

- Messages

- 39

- Helped

- 5

- Reputation

-

10

- Reaction score

- 5

- Trophy points

- 1,288

- Activity points

-

1,467

https://www.fullchipdesign.com/verilog_tutorial.htm

Synchronous Random Access Memory (RAM) implementation in verilog is at following link.

**broken link removed**

-

#13

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

-

#14

- Joined

- Jan 25, 2010

- Messages

- 39

- Helped

- 5

- Reputation

-

10

- Reaction score

- 5

- Trophy points

- 1,288

- Activity points

-

1,467

-

#15

- Joined

- Apr 17, 2012

- Messages

- 10

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

-

1,373

— — — Updated — — —

hey thnx FvM n atulaxc i got the sequential accessing thing…

- Status

- Not open for further replies.

Similar threads

-

Digital Design and Embedded Programming

-

Digital Signal Processing

-

This site uses cookies to help personalise content, tailor your experience and to keep you logged in if you register.

By continuing to use this site, you are consenting to our use of cookies.