-

Ремонт

Сообщение добавил Hlorofos

Все полезные ссылки и FAQ можно найти в первом сообщении. Прежде чем задать вопрос, посмотрите там.

- Назад

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- Далее

-

Страница 103 из 225

Рекомендуемые сообщения

-

- Поделиться

Добрый день. Ищу сервис в г. Тюмень.

S9 одна из плат перестала работать:

chain[5] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Есть еще пара плат работают по несколько часов и отваливаются. Дальше асик на двух работает..

Ссылка на комментарий

Поделиться на другие сайты

-

Ответов

5.6т -

Создана

9 Jun 2016, 11:44 -

Последний ответ

6 Feb 2023, 18:45

Топ авторов темы

-

645

-

415

-

171

-

146

Изображения в теме

-

- Поделиться

Дисплей там только красивая штука, несущая минимум информации. Либо скажет, что на плате нет асиков, хотя какая то часть определяется, либо покажет температуру, и что все ОК, если все чипы на месте. Без него все работает замечательно. По поводу новых контролек не скажу точно, но у меня есть один S9i, и слот под sd карту там распаян. Терминал по UART, все верно. 115200, 8, N, 1.

Изменено 11 Jan 2019, 12:42 пользователем Lomaster

Дополнил

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

3 часа назад, ShurikMMS сказал:

Добрый день. Ищу сервис в г. Тюмень.

S9 одна из плат перестала работать:

chain[5] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]Есть еще пара плат работают по несколько часов и отваливаются. Дальше асик на двух работает..

Проверьте, может шлейф не алё, который на эту плату идет. Контролька не видит PIC. Микрочип сама по себе очень и очень живуч, просто так его не «завалишь». Если шлейф нормальный, возможно перешивка Пика поможет.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

1 час назад, Lomaster сказал:

Дисплей там только красивая штука, несущая минимум информации. Либо скажет, что на плате нет асиков, хотя какая то часть определяется, либо покажет температуру, и что все ОК, если все чипы на месте. Без него все работает замечательно. По поводу новых контролек не скажу точно, но у меня есть один S9i, и слот под sd карту там распаян. Терминал по UART, все верно. 115200, 8, N, 1.

Да запустил уже, спасибо.

Вещь заниательная но больших преимуществ перед зацикленным бимайнером не увидел, ну только дополнительные удобства, хотя надо в конфигах поковыряться может что интересное и есть

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

Народ а подскажите. Перестал работать еще и S9 у меня

В кернел логе пишет такое:

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]

Что за ошибка и как исправить?

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

16 минут назад, zabuza79 сказал:

Народ а подскажите. Перестал работать еще и S9 у меня

В кернел логе пишет такое:

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=a0(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(3) addr_L=80(3) on Chain[4]Что за ошибка и как исправить?

Слетела прошивка PIC на хэш плате. Нужно прошивать контроллер программатором.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

57 минут назад, ASIC REPAIR сказал:

Слетела прошивка PIC на хэш плате. Нужно прошивать контроллер программатором.

И как это сделать? Нужен специальный программатор?

Хэш плата это контрол борд имеется в виду?

Изменено 11 Jan 2019, 15:51 пользователем zabuza79

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

12 минут назад, zabuza79 сказал:

И как это сделать? Нужен специальный программатор?

Хэш плата это контрол борд имеется в виду?

Да, необходим специальный программатор, PICkit 3.

Хэш плата — лезвие, на которой чипы, внутри аппарата, а контрольная — сверху.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

22 минуты назад, ASIC REPAIR сказал:

Да, необходим специальный программатор, PICkit 3.

Хэш плата — лезвие, на которой чипы, внутри аппарата, а контрольная — сверху.

Ну тогда дело не в хэш плате/ах потому что я сейчас переставил верхнюю плату (контрол борд) с рабочего с9, и все 3 внутренние платы заработали. А вот контрол борд соответственно поставленная на исправный майнер опять выдала туже ошибку.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

Только что, zabuza79 сказал:

Ну тогда дело не в хэш плате/ах потому что я сейчас переставил верхнюю плату (контрол борд) с рабочего с9, и все 3 внутренние платы заработали. А вот контрол борд соответственно поставленная на исправный майнер опять выдала туже ошибку.

попробуйте прошить контрольную плату официальной прошивкой с сайта Bitmain

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

10 минут назад, ASIC REPAIR сказал:

попробуйте прошить контрольную плату официальной прошивкой с сайта Bitmain

Пробовал уже несколько прошивок — все туже ошибку выдает.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

4 минуты назад, zabuza79 сказал:

Пробовал уже несколько прошивок — все туже ошибку выдает.

посмотрите разъемы на контрольной плате куда вставляется шлейф, возможно загнуты контакты, попробуйте другой шлейф поставить. Если проблема не устранится — ремонтировать контрольную плату.

Изменено 11 Jan 2019, 16:27 пользователем ASIC REPAIR

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

@zabuza79 + к действиям описанным @ASIC REPAIR осмотрите мелкие резисторы рядом с разъемом на плате управления на предмет их повреждения или окисления (может вода попала) и места пайки разъема на те же дефекты.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

1 час назад, Splinter сказал:

@zabuza79 + к действиям описанным @ASIC REPAIR осмотрите мелкие резисторы рядом с разъемом на плате управления на предмет их повреждения или окисления (может вода попала) и места пайки разъема на те же дефекты.

Ну в общем никаких внешних признаков поломки не обнаружено а с асиком происходит тоже что и с т9 — после нескольких попыток установить разные прошивки он перестал на них как либо реагировать и кроме пустого экрана Овервью ничего не выдает.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

@zabuza79 Т.к. обмен с PIC со всех 3-х хэш плат идет по одному интерфейсу, а их адреса задаются теми самыми мелкими резисторами рядом с разъемом, которые я вас просил посмотреть, и остальные платы работают, то вариант только один — где-то нет контакта. Или на хэш-плату не подается питание 3,3В через тот же самый разъем (опять же проблемы с отсутствием контакта).

Восстанавливайте прошивку с помощью SD-карты. А потом отдайте плату тому, кто сможет прозвонить все контакты и при необходимости их пропаять.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

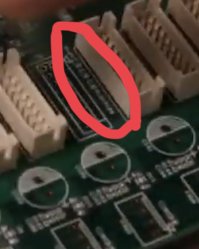

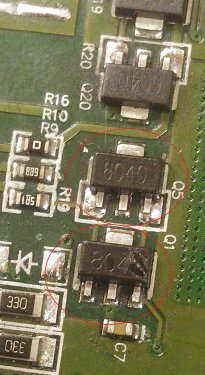

Всем привет. Подскажите, в цепи где шлейф крепиться на лезвие, стоят по 3 smd резистора. Знает кто то их маркировку?

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

Кто знает маркировку smd резистора ?

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

9 часов назад, valmain сказал:

Кто знает маркировку smd резистора ?

Так померяй соседние, все одинаковые они, сопротивление я конечно измерил но думаю этой наводки будет более чем достаточно

Изменено 15 Jan 2019, 07:25 пользователем kip102

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

я замерял, 4.7 кОм. Три модели smd подходят от 0402 и выше

Ссылка на комментарий

Поделиться на другие сайты

- 2 недели спустя…

-

- Поделиться

Всем привет. Antiminer s9 14t. Минут пять работает, потом падает до нуля. Перезагружаю и в се по новой. Причем перезагружается очень быстро. В система в разделе «Hardware Version» сначала висит «Socket connect failed: Connection refused», потом информация о версии отображается. Предполагаю, что отказала управляющая плата. Знающие люди подскажите. Лог файл прилагаю

лог.txt

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

проверить бп, кабель интернета, ну и работоспособность кулеров?

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

блок питания менял, ставил с рабочего асика. все кабели рабочие. кулера рабочие, при неисправности кулера логи были бы другие

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

@user123

Chain[J6] has 63 asic

Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

set_reset_hashboard = 0x00000040

set_reset_hashboard = 0x00000000

retry Chain[J7] has 0 asic

Chain[J8] has 63 asic

J7 у тебя дохлая. Отключи ее и попробуй без нее. Если будет то же, пиши.

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

26.08.2018 в 10:10, kupper68 сказал:

Это копия с тестера на С5 плате..

У кого есть от Xilinx.. т.к последний С5 контроллер держал в руках год назад… или может у кого под официальный тестер на V9 плате есть прошивка

Изменено 28 Jan 2019, 14:49 пользователем dimonhm1

Ссылка на комментарий

Поделиться на другие сайты

-

- Поделиться

Привет, у меня есть S9 hashBoard_V4.21

кто-нибудь может мне помочь, что это?

я знаю, что он получает 12 В, но что получится, если кто-то знает некоторые спецификации или технические данные. Может быть, у кого-то есть принципиальная схема или ее части?

Ссылка на комментарий

Поделиться на другие сайты

-

26 Sep 2021, 10:21

rammendo изменил название на Ремонт: Bitmain Antminer s7, s9, l3+

-

12 Sep 2019, 14:29

Lexis77 закрыл тема

-

4 Jun 2020, 19:25

rammendo закрепил тема

-

4 Jun 2020, 22:35

rammendo сделал не популярным тема

-

6 Jun 2020, 09:08

rammendo популярно и откреплено это тема

- Назад

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- Далее

- Страница 103 из 225

Для публикации сообщений создайте учётную запись или авторизуйтесь

Вы должны быть пользователем, чтобы оставить комментарий

Войти

Уже есть аккаунт? Войти в систему.

Войти

-

Последние посетители

0 пользователей онлайн

- Ни одного зарегистрированного пользователя не просматривает данную страницу

-

Similar Topics

-

Antminer S19, S19pro, S19j, S19a, S19i, S19j Pro, S19 Hyd, S19pro Hyd, S19pro+ Hyd, T19 Hyd

Официальный сайт | Manual | Прошивка (официальный сайт) | Прошивка (bits.media)

В теме действуют все Правила форума!

Перед тем как задать вопрос, посмотрите НОВИЧКИ Bits.Media, все сюда, F.A.Q по майнингу. Уважайте своё и чужое время.

Для обсуждения и поиска программ/драйверов пользуйтесь разделом Файлы.

Сообщения, не относящиеся к теме обсуждения (оффтоп), удаляются без предупреждения.

Технические характеристики:

Статьи на Bits.me

4 Mar 2020, 20:51

в ASIC/FPGA майнеры

-

-

Cherxan

-

8 Feb 2023, 05:23

-

-

Ремонт вентиляторов Antminer s7/s9

Добрый день коллеги. Есть некоторое количество вентиляторов которые снял по причине выхода из строя за N-ое время. Часть работает, но на оборотах 600-700, часть просто не работает. Выбрасывать жалко, руки чешутся.

Кто нибудь занимался мазохизмом по ремонту? Видел на Али вентики с пометкой «Восстановленые». Вопросы:

1. Как снять плату со статором, выдавливать чем? Греть? Как поставить обратно, а то неудобно тыкаться в нее когда она в корпусе.

2. Есть схемка ЭП у кого?

31 Mar 2019, 17:28

в Вентиляция и охлаждение

-

-

svm55

-

1 Feb 2023, 11:09

-

-

Antminer Z11

Официальный сайт | Manual | Прошивка (официальный сайт) | Прошивка (bits.media)

В теме действуют все Правила форума!

Перед тем как задать вопрос, посмотрите НОВИЧКИ Bits.Media, все сюда, F.A.Q по майнингу. Уважайте своё и чужое время.

Для обсуждения и поиска программ/драйверов пользуйтесь разделом Файлы.

Сообщения, не относящиеся к теме обсуждения (оффтоп), удаляются без предупреждения.

Технические характеристики:

Статьи на Bits.me

19 Mar 2019, 06:59

в ASIC/FPGA майнеры

-

-

Splinter

-

31 Jan 2023, 10:55

-

-

Antminer L7

Доброго дня, уважаемые!

Возможно найдётся тот экстремал, кто прикупил данную машину?

Отпишитесь по опыту эксплуатации, а то в голову лезет мысль о покупке.

18 Mar 2022, 07:15

в ASIC/FPGA майнеры

-

-

antoxa42

-

30 Jan 2023, 08:34

-

-

Antminer S17, S17pro, S17+, S17e, T17, T17e, T17+

Официальный сайт | Manual | Прошивка (официальный сайт) | Прошивка (bits.media)

В теме действуют все Правила форума!

Перед тем как задать вопрос, посмотрите НОВИЧКИ Bits.Media, все сюда, F.A.Q по майнингу. Уважайте своё и чужое время.

Для обсуждения и поиска программ/драйверов пользуйтесь разделом Файлы.

Сообщения, не относящиеся к теме обсуждения (оффтоп), удаляются без предупреждения.

Технические характеристики:

Статьи на Bits.me

8 Jun 2019, 07:15

в ASIC/FPGA майнеры

-

-

peepoo

-

20 Jan 2023, 12:49

-

-

legendary

Activity: 2744

Merit: 2373

Bull market is coming?

Where can I find the April firmware?

Have you tried to flash it with s9_fix_upgrade.tar.gz first before you flash it with other firmware? It might solve the issue.

But if it doesn’t work you can try the april firmware just found it from here https://bitcointalksearch.org/topic/m.36124081

it’s exactly the same problem as with my T9 +, see my subject;)

In your case, I am 99.9% sure that with the PicKit3 you bring back to life your card!

1: extract the HEX file from a functioning card

2: the reinjected into the card that does not work (FW 0X00)

Ps : the PicKit3, the cost is ~_ 25USD

I agree with this I found his thread from here https://bitcointalksearch.org/topic/repair-a-t9-after-a-bad-firmware-lost-chain-5032987 flashing the hashboard with working hex file might solve the issue.

sr. member

Activity: 440

Merit: 325

it’s exactly the same problem as with my T9 +, see my subject;)

In your case, I am 99.9% sure that with the PicKit3 you bring back to life your card!

1: extract the HEX file from a functioning card

2: the reinjected into the card that does not work (FW 0X00)

Ps : the PicKit3, the cost is ~_ 25USD

newbie

Activity: 20

Merit: 0

Sounds like your PIC error is only on one board. Flashing the April firmware let you ignore that error and continue to mine with the other two boards.

If you want to, you can replace the PIC on the faulty board with one from a spare board if you want to. Bitmain doesn’t seem to sell spare PICs. Also, try replacing the ribbon cable to the board giving you the issue.

Where can I find the April firmware?

full member

Activity: 538

Merit: 172

I would like to know how you did to solve the failure, since when updating the FIRMWARE it is not coencted but when changing for an anterior it only connects with two (2) cards and lowers the HASH rate.

Sounds like your PIC error is only on one board. Flashing the April firmware let you ignore that error and continue to mine with the other two boards.

If you want to, you can replace the PIC on the faulty board with one from a spare board if you want to. Bitmain doesn’t seem to sell spare PICs. Also, try replacing the ribbon cable to the board giving you the issue.

newbie

Activity: 4

Merit: 0

Hello BliksemMiner

I am Rainer and I am also a miner with an ANTMINER S9 of 13.50T and I have the same problem you have or had:

Check chain [5] PIC fw version = 0x00

chain [5] PIC need restore …

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

Error of set PIC FLASH addr: addr_H = 3 (0) addr_L = 0 (0) on Chain [5]

After restore: chain [5] PIC fw version = 0x00

I would like to know how you did to solve the failure, since when updating the FIRMWARE it is not coencted but when changing for an anterior it only connects with two (2) cards and lowers the HASH rate.

You can help me please, if it is possible for you to send me the firmware you used or still present the flaw.

Atte.

Rainer

full member

Activity: 538

Merit: 172

I see this issue almost daily. Usually rolling back the firmware will let you run while ignoring the issue.

If a board is zero you can replace the PIC with one from a spare board if you want to. Bitmain doesn’t seem to sell spare PICs.

I have also seen the issue happen because of a faulty ribbon cable. Try replacing the ribbon cable to the board giving you the issue.

If you get the 413 error when flashing firmware, use a microSD to flash manually.

legendary

Activity: 2030

Merit: 1076

BTCLife.global participant

Doesn’t look like this. I can log in to web interface, I see the kernel Log, I can reboot the miner etc.

legendary

Activity: 2744

Merit: 2373

Bull market is coming?

Guys, April firmware does not help me, still Error of set PIC FLASH addr… I tried completely different PSUs, I left only one hashing board connected to controller and to PSU, but still nothing.

Please help me somebody…

It might be the control board is bricked since, the April firmware doesn’t work the only way you can do now is to reflash the whole control board to fix the issue.

Please read this https://bitcointalksearch.org/topic/rescuing-a-bricked-t9-and-s9-control-board-howto-2386296

full member

Activity: 538

Merit: 172

Probably something wrong with the hashboard.

You can always try using the package to fix fw upgrade, flash it to SD card, move the jumper pin and flash using microSD. (Flashing the april firmware of course).

legendary

Activity: 2030

Merit: 1076

BTCLife.global participant

Guys, April firmware does not help me, still Error of set PIC FLASH addr… I tried completely different PSUs, I left only one hashing board connected to controller and to PSU, but still nothing.

Please help me somebody…

full member

Activity: 538

Merit: 172

The interesting thing is that there is zero hashing with the 1117 firmware and with April firmware only 2 boards work. What other previous versions do you recommend I try out?

Scared to fiddle in case they totally stop working.

I wouldn’t try any other firmware besides the one from April. There’s probably something wrong with the third board.

newbie

Activity: 10

Merit: 0

The interesting thing is that there is zero hashing with the 1117 firmware and with April firmware only 2 boards work. What other previous versions do you recommend I try out?

Scared to fiddle in case they totally stop working.

full member

Activity: 538

Merit: 172

Common problem on the 1117 firmware. Roll it back to an older official firmware and your problem should go away.

^This. But, it seems like you have already have tried flashing the older firmware.

name: Antminer-S9-all-201704270135-autofreq-user-Update2UBI-NF.tar.gz

sha-1: 0515029015ad8dcedb185367fc5f829851dc65ed

With latest firmware Fri Nov 17 17:57:49 CST 2017 I do Not see a Hardware Version and BMminer version and zero hashing on any of the boards

When I load up firmware version from April 2017 I see 2 boards and they hash but not on antpool only on nicehash.

It sounds like at least the other 2 boards should work now. Try unplugging the faulty board and see if the miner will hash natively using the other two.

hero member

Activity: 756

Merit: 560

Common problem on the 1117 firmware. Roll it back to an older official firmware and your problem should go away.

newbie

Activity: 10

Merit: 0

Hi All

Issues with my Antminer S9…

Is one of my boards fried?

With latest firmware Fri Nov 17 17:57:49 CST 2017 I do Not see a Hardware Version and BMminer version and zero hashing on any of the boards

When I load up firmware version from April 2017 I see 2 boards and they hash but not on antpool only on nicehash.

Kernel log below…

Check chain[5] PIC fw version=0x00

chain[5] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

After restore: chain[5] PIC fw version=0x00

Thanks in advance for your insight.

Regards

Bliksem

Topic: S9i with driver-bitmain.c:5474: Error of set PIC FLASH. (Read 589 times)

Be very careful with that HEX file. It is only supposed to be used on the T9+. See quote below from that thread:

Hello guys i had the (chain[5] PIC need restore . ) error and fixed it by using the IP Reporter Firmware restore, you can find it in Bitmain’s Forum but i leave it here for all of you

IP Reporter Restore (The miner will automatically revert to factory default firmware)

This method is only applicable to the miner as below. (The SD card slot of the miner should be on the left of Ethernet interface.

Usage: Please power off the miner, then hold down the IP Reporter and don’t release it. At the same time, please power on the miner. Releasing the IP Reporter after 5 seconds, the machine will automatically restore factory settings.

NOTE: This method is not applicable to the miner which has a SD card on the right of the Ethernet interface.

This is just a method to do a factory reset this sometimes works but not all and you are just copy pasted the guide from bitmain support without credit.

Anyway, you can find this method from here «How to reset miner to factory settings » credited to bitmain.

This is just a basic solution but if the restore factory reset doesn’t work you can try the method below.

The method to fix this issue if you have PIC error is to flashing it with PICKit 3 which is tested by some miners out there.

You can find this method from here https://bitcointalksearch.org/topic/repair-a-t9-after-a-bad-firmware-lost-chain-5032987

Hello guys i had the (chain[5] PIC need restore . ) error and fixed it by using the IP Reporter Firmware restore, you can find it in Bitmain’s Forum but i leave it here for all of you

IP Reporter Restore (The miner will automatically revert to factory default firmware)

This method is only applicable to the miner as below. (The SD card slot of the miner should be on the left of Ethernet interface.

Usage: Please power off the miner, then hold down the IP Reporter and don’t release it. At the same time, please power on the miner. Releasing the IP Reporter after 5 seconds, the machine will automatically restore factory settings.

NOTE: This method is not applicable to the miner which has a SD card on the right of the Ethernet interface.

This issue has been bugging me for some time.

I finally fixed one (by chance?) today. What I did was unplug the chain/board giving the error, flashed the same firmware through the web «Upgrade» page, let it boot, then plugged the board back in and rebooted. Full hash now.

So strange

This issue has been bugging me for some time.

I finally fixed one (by chance?) today. What I did was unplug the chain/board giving the error, flashed the same firmware through the web «Upgrade» page, let it boot, then plugged the board back in and rebooted. Full hash now.

So strange

I just started experiencing the same problem as well.

I’ve tried all of the following and still zero hashing:

1. Flashing my s9i with s9i firmware downloaded from Bitmain website

2. Flashing my s9i to latest s9 firmware

3. Flashing my s9i to older s9 firmware

Seems there is just no fix for this right now.

I have the same issue, blank hardware version and bmminer version. Also version S9i_VTest (which doesn’t seems right to me)

Does anyone have version Tue Mar 13 10:15:18 CST 2018? S9i_V2.05 This one is currently running on my other miners without a problem.

I am super slow.

As per your advice, I just got around to creating a support ticket with Bitmain, rather than proactively swapping out the control board without «permission.»

Wishing you luck on your RMA experience! I will keep my experience posted here as well!

Just shipped the S9i out to Bitmain repair facility in Washington (state). Better than having to send back to China — should be faster and definitely cheaper. Hate to loose the processing time and downtime with testing though.

Well, hopefully it comes back happy and working!

Oh, and be careful try to swap controllers if you want to try this. They made a point in submittin the repair ticket that tearing the warranty seal will void the warranty — unless Bitmain support actually told you to do so. In my case, I should be good since they told me to do it, but others on here might not be so lucky if you can’t show that their support personel told you too. You can’t swap the controllers without tearing one of their warranty tapes as they put it over one of the screws on the fan shroud plat, which has to be remove to get the controllers on/off.

Well, this did not help. I swapped an S9 controller into the S9i, re-flashed the firmware to the S9i firmware link they provided — and still the same issue!

I did also re-flash the original S9i controller with S9 firmware while in my S9 that I pulled the controller from for the S9i. It worked fine. So definitely the controller is good — well, at least it functions in the S9.

I flashed the controller in the S9i back to S9 firmware and flashed S9i firmware on the controller in the S9 and then swapped the controllers back to their original miners. This time when I flashed the S9i firmware, I did it WITHOUT keeping the previous settings to see it that would help. NOPE! Still the same issue!

Both machines booted with the improper firmware flashed to them (S9i firmware on S9 and S9 firmware on S9i). The S9 (with the S9i firmware) got similar PIC errors and would not start BMMiner — thus no mining would occur. Once the S9 had its S9 firmware back — it went back to mining just fine. But I still have a non-mining toaster for an S9i.

If this is a software fix, it would really suck to have to send it back to Bitmain in China.

Doesn’t Bitmain have a warranty place here in the US, like in California or something? I think their next step is going to be to have me to send it back.

Unless anyone else has any other ideas?

I am having the exact same issue that you describe.

driver-bitmain.c:5474: Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

I thought I would try what your last post recommended, swapping an S9 control board for the S9i in question, and reflashing the firmware with the S9i firmware. . .

But how the heck do you get the control board out.

After removing all the cords, I pop the clips and begin to slide it out of the back, but it bumps into the hashing boards.

Do I have to unscrew the small control-board metal faceplate and slide it out of the front. . . ? I will research more . . .

I am following your issue since we seem to be having the same one. Have you tried this control board swap yet? Did it work?

They gave directions and a link to a YouTube video showing the process. Here is their response telling me what to do here:

You could use the S9 controller but be sure to reflash the S9i firmware https://shop.bitmain.com/support.htm?pid=00720180525135351672WCe9WPkv06BF

How to disassemble and reassemble S9/T9 control boards:

1. Unplug the fans and flat cable. Please handle the clip-on plug carefully.

2. Remove the four mounting screws of the fan shroud and put aside the fan. Keep the screws in a safe place.

3. Remove the control board from the card slot.

4. Push aside the two leaf springs and remove the control board.

5. To install the control board reverse the above steps.

Please let us know if you have additional questions or concerns.

If you get this done before me please post your results. I may get to it tonight, but maybe not until as late as Sunday evening.

I am having the exact same issue that you describe.

driver-bitmain.c:5474: Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[5]

I thought I would try what your last post recommended, swapping an S9 control board for the S9i in question, and reflashing the firmware with the S9i firmware. . .

But how the heck do you get the control board out.

After removing all the cords, I pop the clips and begin to slide it out of the back, but it bumps into the hashing boards.

Do I have to unscrew the small control-board metal faceplate and slide it out of the front. . . ? I will research more . . .

I am following your issue since we seem to be having the same one. Have you tried this control board swap yet? Did it work?

First off, the bitmain response is essentially worthless boilerplate and unrelated to your problem, so you can ignore it.

Basically, the S9i firmware and the newer S9 firmware will hang and stop booting when this error is encountered. On the S9, you can work around this issue by installing a previous version of the firmware. Unfortunately, that doesn’t help you since you need S9i firmware. Perhaps bitmain warranty rma is your only option, although there must be some fix for this that I’m not aware of.

More or less — that’s what I thought. I have gotten another message from them after I updated them with answers to their test list. Now they want me to take an S9 controller board and swap it out with the controller board on this S9i — then re-flash it with the S9i firmware from their site. If that works, then they will send me a replacement controller. Does that make sense? I don’t know what these PIC things are — so not sure if this is a viable solution/test. If the PICs are on the controller, then I suppose this would make sense and this test would verify if there’s some kind of controller flaw.

Not sure why going to an older version of the firmware with the S9’s would solve this — unless the newer firmware is trying to do something particular with the controller that the older firmware is not. Maybe for efficiency purposes? Maybe this could truly indicate a problem with the controller that simply isn’t noticed with an older firmware. Anyway, now I have to go through this process to see if it helps. If the S9 controller works — I wonder if I couldn’t re-flash the S9i controller with the S9 firmware and literally just swap the controllers. Maybe use an earlier version of the S9 firmware if it shows the same issue. If that works then could have them up faster while they have a controller on the way.

Источник

Hello there, I have recently bought a Antminer t9, and I am having some problems, the board says :

Hardware Version Socket connect failed: Connection refused.

I have :

-

rebooted

-

Let it run for more than one hour ( And the button at the front where it says normal ) starts glowing green, but my miner is not mining.

I have to say that when i first plugged it in, it was working, but when I chagned the address to nice hash while it said no hashing detected on the board apprently nicehash got something for couple of minutes )

Now my problem is I am kinda stuck what to do.

oh and Kernel Log keeps saying :

Check chain[1] PIC fw version=0x00 chain[1] PIC need restore … Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] After restore: chain[1] PIC fw version=0x00 chain[1] PIC need restore … Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[1] After restore: chain[1] PIC fw version=0x00 Check chain[2] PIC fw version=0x00 chain[2] PIC need restore … Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] After restore: chain[2] PIC fw version=0x00 chain[2] PIC need restore … Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2] Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[2]

Anybody had similar issues ,and fix

Thank you for your time

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 3.14.0-xilinx-gb190cb0-dirty ([email protected]) (gcc version 4.8.3 20140320 (prerelease) (Sourcery CodeBench Lite 2014.05-23) ) #57 SMP PREEMPT Fri Dec 9 14:49:22 CST 2016

[ 0.000000] CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=18c5387d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] Machine model: Xilinx Zynq

[ 0.000000] cma: CMA: reserved 128 MiB at 27800000

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] On node 0 totalpages: 258048

[ 0.000000] free_area_init_node: node 0, pgdat c0740a40, node_mem_map e6fd8000

[ 0.000000] Normal zone: 1520 pages used for memmap

[ 0.000000] Normal zone: 0 pages reserved

[ 0.000000] Normal zone: 194560 pages, LIFO batch:31

[ 0.000000] HighMem zone: 496 pages used for memmap

[ 0.000000] HighMem zone: 63488 pages, LIFO batch:15

[ 0.000000] PERCPU: Embedded 8 pages/cpu @e6fc0000 s9088 r8192 d15488 u32768

[ 0.000000] pcpu-alloc: s9088 r8192 d15488 u32768 alloc=8*4096

[ 0.000000] pcpu-alloc: [0] 0 [0] 1

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 256528

[ 0.000000] Kernel command line: noinitrd mem=1008M console=ttyPS0,115200 root=ubi0:rootfs ubi.mtd=1 rootfstype=ubifs rw rootwait

[ 0.000000] PID hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

[ 0.000000] Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

[ 0.000000] Memory: 884148K/1032192K available (5032K kernel code, 283K rwdata, 1916K rodata, 204K init, 258K bss, 148044K reserved, 253952K highmem)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 — 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xfff00000 — 0xfffe0000 ( 896 kB)

[ 0.000000] vmalloc : 0xf0000000 — 0xff000000 ( 240 MB)

[ 0.000000] lowmem : 0xc0000000 — 0xef800000 ( 760 MB)

[ 0.000000] pkmap : 0xbfe00000 — 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 — 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 — 0xc06d1374 (6949 kB)

[ 0.000000] .init : 0xc06d2000 — 0xc0705380 ( 205 kB)

[ 0.000000] .data : 0xc0706000 — 0xc074cf78 ( 284 kB)

[ 0.000000] .bss : 0xc074cf84 — 0xc078d9fc ( 259 kB)

[ 0.000000] Preemptible hierarchical RCU implementation.

[ 0.000000] Dump stacks of tasks blocking RCU-preempt GP.

[ 0.000000] RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.

[ 0.000000] RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2

[ 0.000000] NR_IRQS:16 nr_irqs:16 16

[ 0.000000] ps7-slcr mapped to f0004000

[ 0.000000] zynq_clock_init: clkc starts at f0004100

[ 0.000000] Zynq clock init

[ 0.000015] sched_clock: 64 bits at 333MHz, resolution 3ns, wraps every 3298534883328ns

[ 0.000306] ps7-ttc #0 at f0006000, irq=43

[ 0.000614] Console: colour dummy device 80×30

[ 0.000651] Calibrating delay loop… 1332.01 BogoMIPS (lpj=6660096)

[ 0.090251] pid_max: default: 32768 minimum: 301

[ 0.090470] Mount-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.090492] Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.092635] CPU: Testing write buffer coherency: ok

[ 0.092984] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.093044] Setting up static identity map for 0x4c4af8 — 0x4c4b50

[ 0.093268] L310 cache controller enabled

[ 0.093288] l2x0: 8 ways, CACHE_ID 0x410000c8, AUX_CTRL 0x72760000, Cache size: 512 kB

[ 0.171035] CPU1: Booted secondary processor

[ 0.260228] CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

[ 0.260357] Brought up 2 CPUs

[ 0.260376] SMP: Total of 2 processors activated.

[ 0.260384] CPU: All CPU(s) started in SVC mode.

[ 0.261033] devtmpfs: initialized

[ 0.263437] VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

[ 0.264637] regulator-dummy: no parameters

[ 0.272345] NET: Registered protocol family 16

[ 0.274637] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.276908] cpuidle: using governor ladder

[ 0.276922] cpuidle: using governor menu

[ 0.284318] syscon f8000000.ps7-slcr: regmap [mem 0xf8000000-0xf8000fff] registered

[ 0.285827] hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

[ 0.285841] hw-breakpoint: maximum watchpoint size is 4 bytes.

[ 0.285954] zynq-ocm f800c000.ps7-ocmc: ZYNQ OCM pool: 256 KiB @ 0xf0080000

[ 0.307604] bio: create slab <bio-0> at 0

[ 0.309011] vgaarb: loaded

[ 0.309725] SCSI subsystem initialized

[ 0.310691] usbcore: registered new interface driver usbfs

[ 0.310861] usbcore: registered new interface driver hub

[ 0.311211] usbcore: registered new device driver usb

[ 0.311737] media: Linux media interface: v0.10

[ 0.311891] Linux video capture interface: v2.00

[ 0.312129] pps_core: LinuxPPS API ver. 1 registered

[ 0.312141] pps_core: Software ver. 5.3.6 — Copyright 2005-2007 Rodolfo Giometti <[email protected]>

[ 0.312262] PTP clock support registered

[ 0.312621] EDAC MC: Ver: 3.0.0

[ 0.313651] Advanced Linux Sound Architecture Driver Initialized.

[ 0.316487] DMA-API: preallocated 4096 debug entries

[ 0.316500] DMA-API: debugging enabled by kernel config

[ 0.316577] Switched to clocksource arm_global_timer

[ 0.336325] NET: Registered protocol family 2

[ 0.337142] TCP established hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.337242] TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.337401] TCP: Hash tables configured (established 8192 bind 8192)

[ 0.337463] TCP: reno registered

[ 0.337481] UDP hash table entries: 512 (order: 2, 16384 bytes)

[ 0.337530] UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

[ 0.337814] NET: Registered protocol family 1

[ 0.338185] RPC: Registered named UNIX socket transport module.

[ 0.338197] RPC: Registered udp transport module.

[ 0.338206] RPC: Registered tcp transport module.

[ 0.338214] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.338227] PCI: CLS 0 bytes, default 64

[ 0.338666] hw perfevents: enabled with ARMv7 Cortex-A9 PMU driver, 7 counters available

[ 0.340662] futex hash table entries: 512 (order: 3, 32768 bytes)

[ 0.342053] bounce pool size: 64 pages

[ 0.342951] jffs2: version 2.2. (NAND) В© 2001-2006 Red Hat, Inc.

[ 0.343145] msgmni has been set to 1486

[ 0.343922] io scheduler noop registered

[ 0.343936] io scheduler deadline registered

[ 0.343976] io scheduler cfq registered (default)

[ 0.353330] dma-pl330 f8003000.ps7-dma: Loaded driver for PL330 DMAC-2364208

[ 0.353350] dma-pl330 f8003000.ps7-dma: DBUFF-128x8bytes Num_Chans-8 Num_Peri-4 Num_Events-16

[ 0.475990] e0001000.serial: ttyPS0 at MMIO 0xe0001000 (irq = 82, base_baud = 3124999) is a xuartps

[ 1.048994] console [ttyPS0] enabled

[ 1.053268] xdevcfg f8007000.ps7-dev-cfg: ioremap 0xf8007000 to f0068000

[ 1.060917] [drm] Initialized drm 1.1.0 20060810

[ 1.077849] brd: module loaded

[ 1.087222] loop: module loaded

[ 1.096677] e1000e: Intel(R) PRO/1000 Network Driver — 2.3.2-k

[ 1.102427] e1000e: Copyright(c) 1999 — 2013 Intel Corporation.

[ 1.110404] libphy: XEMACPS mii bus: probed

[ 1.114772] ————- phy_id = 0x3625e62

[ 1.119820] xemacps e000b000.ps7-ethernet: pdev->id -1, baseaddr 0xe000b000, irq 54

[ 1.128464] ehci_hcd: USB 2.0 ‘Enhanced’ Host Controller (EHCI) Driver

[ 1.135084] ehci-pci: EHCI PCI platform driver

[ 1.142319] zynq-dr e0002000.ps7-usb: Unable to init USB phy, missing?

[ 1.149151] usbcore: registered new interface driver usb-storage

[ 1.155998] mousedev: PS/2 mouse device common for all mice

[ 1.162190] i2c /dev entries driver

[ 1.169199] zynq-edac f8006000.ps7-ddrc: ecc not enabled

[ 1.174680] cpufreq_cpu0: failed to get cpu0 regulator: -19

[ 1.180595] Xilinx Zynq CpuIdle Driver started

[ 1.185439] sdhci: Secure Digital Host Controller Interface driver

[ 1.191605] sdhci: Copyright(c) Pierre Ossman

[ 1.195876] sdhci-pltfm: SDHCI platform and OF driver helper

[ 1.202738] mmc0: no vqmmc regulator found

[ 1.206782] mmc0: no vmmc regulator found

[ 1.246595] mmc0: SDHCI controller on e0100000.ps7-sdio [e0100000.ps7-sdio] using ADMA

[ 1.255264] usbcore: registered new interface driver usbhid

[ 1.260780] usbhid: USB HID core driver

[ 1.265479] nand: device found, Manufacturer ID: 0x2c, Chip ID: 0xda

[ 1.271770] nand: Micron MT29F2G08ABAEAWP

[ 1.275744] nand: 256MiB, SLC, page size: 2048, OOB size: 64

[ 1.281698] Bad block table found at page 131008, version 0x01

[ 1.287912] Bad block table found at page 130944, version 0x01

[ 1.293965] 3 ofpart partitions found on MTD device pl353-nand

[ 1.299729] Creating 3 MTD partitions on «pl353-nand»:

[ 1.304835] 0x000000000000-0x000002000000 : «BOOT.bin-env-dts-kernel»

[ 1.312894] 0x000002000000-0x00000b000000 : «angstram-rootfs»

[ 1.320200] 0x00000b000000-0x000010000000 : «upgrade-rootfs»

[ 1.329141] TCP: cubic registered

[ 1.332374] NET: Registered protocol family 17

[ 1.337106] Registering SWP/SWPB emulation handler

[ 1.342992] regulator-dummy: disabling

[ 1.347334] UBI: attaching mtd1 to ubi0

[ 1.871705] UBI: scanning is finished

[ 1.883315] UBI: attached mtd1 (name «angstram-rootfs», size 144 MiB) to ubi0

[ 1.890392] UBI: PEB size: 131072 bytes (128 KiB), LEB size: 126976 bytes

[ 1.897155] UBI: min./max. I/O unit sizes: 2048/2048, sub-page size 2048

[ 1.903819] UBI: VID header offset: 2048 (aligned 2048), data offset: 4096

[ 1.910697] UBI: good PEBs: 1152, bad PEBs: 0, corrupted PEBs: 0

[ 1.916677] UBI: user volume: 1, internal volumes: 1, max. volumes count: 128

[ 1.923785] UBI: max/mean erase counter: 9/5, WL threshold: 4096, image sequence number: 1324196393

[ 1.932827] UBI: available PEBs: 0, total reserved PEBs: 1152, PEBs reserved for bad PEB handling: 40

[ 1.942044] UBI: background thread «ubi_bgt0d» started, PID 1080

[ 1.942049] drivers/rtc/hctosys.c: unable to open rtc device (rtc0)

[ 1.945966] ALSA device list:

[ 1.945970] No soundcards found.

[ 1.962393] UBIFS: background thread «ubifs_bgt0_0» started, PID 1082

[ 1.991214] UBIFS: recovery needed

[ 2.087267] UBIFS: recovery completed

[ 2.090937] UBIFS: mounted UBI device 0, volume 0, name «rootfs»

[ 2.096880] UBIFS: LEB size: 126976 bytes (124 KiB), min./max. I/O unit sizes: 2048 bytes/2048 bytes

[ 2.105975] UBIFS: FS size: 128626688 bytes (122 MiB, 1013 LEBs), journal size 9023488 bytes (8 MiB, 72 LEBs)

[ 2.115878] UBIFS: reserved for root: 0 bytes (0 KiB)

[ 2.120918] UBIFS: media format: w4/r0 (latest is w4/r0), UUID 6CA47D8E-59BD-4890-B015-0FA8ABA33684, small LPT model

[ 2.131973] VFS: Mounted root (ubifs filesystem) on device 0:11.

[ 2.139164] devtmpfs: mounted

[ 2.142268] Freeing unused kernel memory: 204K (c06d2000 — c0705000)

[ 2.942750] random: dd urandom read with 0 bits of entropy available

[ 3.186635]

[ 3.186635] bcm54xx_config_init

[ 3.786626]

[ 3.786626] bcm54xx_config_init

[ 6.787458] xemacps e000b000.ps7-ethernet: Set clk to 24999999 Hz

[ 6.793549] xemacps e000b000.ps7-ethernet: link up (100/FULL)

[ 19.845992] In axi fpga driver!

[ 19.849085] request_mem_region OK!

[ 19.852456] AXI fpga dev virtual address is 0xf01fe000

[ 19.857583] *base_vir_addr = 0xfc510

[ 19.867404] In fpga mem driver!

[ 19.872736] request_mem_region OK!

[ 19.876340] fpga mem virtual address is 0xf3000000

[ 20.896034]

[ 20.896034] bcm54xx_config_init

[ 22.125936]

[ 22.125936] bcm54xx_config_init

[ 25.126417] xemacps e000b000.ps7-ethernet: Set clk to 24999999 Hz

[ 25.132431] xemacps e000b000.ps7-ethernet: link up (100/FULL)

[ 158.713714] random: nonblocking pool is initialized

Detect 1GB control board of XILINX

Miner Type = S9

Miner compile time: Wed Jun 10 11:48:25 CST 2020 type: Antminer S9 (vnish 3.8.6)

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x00000000

set_reset_allhashboard = 0x0000ffff

set_reset_allhashboard = 0x0000ffff

Checking fans!

1 fan ok

2 fan ok

set_reset_allhashboard = 0x0000ffff

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[0]

Check chain[0] PIC fw version=0x00

chain[0] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

After restore: chain[0] PIC fw version=0x00

chain[0] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[0]

After restore: chain[0] PIC fw version=0x00

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=f(0) addr_L=e8(0) on Chain[4]

Check chain[4] PIC fw version=0x00

chain[4] PIC need restore …

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

Error of set PIC FLASH addr: addr_H=3(0) addr_L=0(0) on Chain[4]

На чтение 15 мин Просмотров 5.7к. Опубликовано 14.03.2020

Содержание

- Comments

- nicson1989

- pyhtin79

- lasthiter

- iDekabrist

- pyhtin79

1.

Issue: The miner has no hash rate. One of the hash board’s temperature exceeds 80 degree Celsius.

Reason: A piece of heat sink is loose or dropped off.

Solution: Remove the hash board that exceeds 80 degree Celsius to repair.

Note: If large quantity of hash boards temperature exceeds 80 degree Celsius, please add cooling devices, as the high temperature will ultimately go into the high temperature protection mode and the miner will shut down. Moreover, the miner can easily get defective when working in a high temperature environment.

2.

Issue: The hash rate is good, but there is no temperature shown on the Miner status.

The hash board is easily burnt if there is no temperature shown for monitoring or when the real temperature is very high

Reason: The temperature detector is damaged on one of the hash boards that lead to the other two hash boards to have the issues on temperature display as well.

Solution: Test the 3 hash boards one by one by connecting to the control board and let it run for about 5 minutes, find the faulty hash board with temperature detection problem and ship it back to repair.

3.

Issue: The hash rate is lower than normal. There is an “X” shown on the Miner status.

Reason: The ASIC chip is damaged, which resulted in the loss of some hash rate on the hash board.

Solution: If that hash board can still work well, you can keep and continue to let it work. There is no need to repair it unless the hash board becomes totally defective.

4.

Issue: The hash rate is lower than normal. There are a lot of “X” shown on Miner status

Reason: The chips are damaged, which lead to the entire hash board running abnormally.

Solution: Remove the hash board to repair.

5.

Issue: The hash rate is lower than normal. There are a lot of “-” shown on Miner status

Reason: It may be caused by instability of the PSU voltage or a defective hash board.

Solution: Replace the PSU and control board-hash board 18 pin ribbon cable. If replacing didn’t work, please remove the hash board to repair.

6.

Issue: The hash rate is lower than normal. Some chips are lost. The hash rate is only running at 2/3 of the normal.

Reason: Chain scission of chips

Solution: Remove the hash board to repair.

7.

Issue: The miner has no hash rate. There is X.X.X.X shown on the Hardware Version. Hash board cannot be detected. There is no information shown at all on the Miner status interface.

Cause: The firmware of miner is not detected.

Solution: Power off the miner and reset it. Reload the firmware.

8.

Issue: The miner worked great when it was powered. After awhile, there is no hash rate.

Reason: One of the fans is not detected. Miner will work well only when both fans are detected.

Solution: Switch the control board connection between the two fans to find out which one is defective.

9.

Issue: A large number of Antpools surfaced. Hash rate is normal. There is no use resetting the router.

Reason: One of the computers in the network has been infected by virus or malware.

Solution: Find infected computer and remove the virus or malware.

10.

Issue: Miner can’t find IP. Red light flashing; Green light does not blink

— Reason:The Miner is not connected with the Internet.

Solution: Test the Internet cable, connection and the settings of the Internet (DHCP mode is required).

— Reason: The miner program has not started.

Solution: Reset the miner several times.

— Reason: The application of miner is lost.

Solution: Perform control board recovery

11.

Issue: The miner doesn’t work after powering on despite changing the PSU.

— Reason: There is a short circuit inside one of the hash boards.

Solution: Find which hash board is defective. Remove the defective part to repair.

— Reason: Control board failure

Solution: Change the control board

12.

Issue: PSU can’t work when if the PSU fan is running. Miner works well after changing PSU.

Reason: The PSU is defective. The PSU fan is powered by a different output. The defect can’t be judged by whether the fan rotation power is normal.

Solution: Ship back the PSU to repair.

13.

Issue: Miner restores to factory setting after powering off.

Reason:The software in BB board is damaged.

Solution: Perform control board recovery

14.

Issue: Miners work well for several month before it starts to malfunction.

— Reason: The hash boards were corroded by humidity and lots of dust.

Solution: Remove the defective hash boards, dust the miner and reduce air humidity.

— Reason: Large amount of dust, resulting in congestion in the air duct. Heat can’t be dissipated. Catkins are likely to cause congestion in air duct.

Solution: Remove the defective hash boards, dust the miner and add dust elimination.

15.

Issue: The machine is defective when network changed

Reason: Due to the network setup, miner can’t find the IP.

Solution: Power off and reset the miner.

Issue: S7 malfunction after running for a while. It runs again after rebooting.

-Reason: Temperature exceeds 80 degree Celsius and miner will automatically shut down.

Solution: Increase the amount of air flow.

— Reason: The PGA in BB board weld badly, which lead to miner’s shut down.

Solution: Remove the BB board to repair.

17.

Issue: PSU can’t work but fan is running. All the indicators are off.

Reason: The control board cannot get power as the power circuit in IO board is damaged.

Solution: Switch the BB Board and IO Board with good miner to troubleshoot the defective parts.

how this my issue

Hi, mi new S9 it doesnt works with the 3 has board, i can see one of them in the miner status. What can i do?

Hi, my S9 after working a few weeks is only detecting 2 hashboards. I tried switching the hashboard to a good miner and wasn’t detected either. Also switched a good hashboard to the bad miner, and was working Ok. I believe the hashboard is broken, I can’t get it detected in any of my miners. Should I send it to repair?

If you have not already done so please email us at support@bitmain.com. We can help you with your specific issue.

I’m having trouble with Issue #7. I get the hardware version x.x.x.x and no «miner status» information. however, when i run a reset, the information is shown for a while, about 01 minute then it goes blank again. The information shown with the default settings is between normal, no x’s found on ACIS Status, and Temperature around 50ºC.

I’ve been looking for a firmware update, but i’m not sure wich one to install. Curious thing, I own 02 Antminers S7, and both came up with the same issue at the same time. so i do not think it is related to hardware problems

Any information you can provide will be very helpful

Hi Rafael. Thank you for submitting a ticket. I have responded to the ticket with the information that you requested.

Hi, i have an S9, and one of the boards showme a lots of «x», then i restart my miner, from the control panel, now the board doesnt turn on. Only two of the 3 boards turns on the red led in the board, and the damaged card does’nt start, load or turn on. I need to remove the damaged board to send it bitmain. Please help.

I have my s7 cards have been damaging, sometimes when the frequency of 700 to 600 step back on sometimes not and in one of the cases the card comes on but the s7 does not have the same power does not reach 4.73

note:in this example the machine had only on card put it at 600 and set the 3 then appeared 3 lit and at the time under the speed restart it and put it in 700 and was thus

note: in this case the only way to start the first card was to put the frequency in 600 and yet not hashea at the speed that should

so I have several cases as well and need to find a solution because you will understand I made an investment and thus won’t be able to recover it

All 17 of my miners stopped working at the same time and now say «socket connection failed. » Please help!

Good morning, I request your help since my S9 has presented a problem.

The temperature of the third hashboard is no longer displayed and two groups of zeros have disappeared in the ASIC state. This has caused the hash rate to be less than normal, obviously the hashboard does not work properly.

Reset the S9 and the values will not be reactivated.

What can I do to resolve this situation? What is happening?

I am able to get a IP address on my L3+ But I am unable to connect via the PC to the Backdoor portal . Air in fan spins at startup the exhaustr fans spins toward the end of the boot process at high speed only. the inter net lights flash green then they go out then come back and then I get a Blinking red light and it turns into a solid red light. PLEASE PLEASE Help Me. Most gracious.

Hi, please submit a support ticket so that we can help you troubleshoot. You can submit the ticket right from our web site.

I have a problem. Chain # 6 is not shown in the tabs «Miner status».

Chain # 7 does not show the temperature of chip 1 and chip 2.

GH / s (rt) — 10995.

I turn on the s9, the red led light on the chain # 6

.

What should I order for repair? I still have a guarantee.

Same issue for me #6. One of my hashing boards does not show up or work anymore. It seems many of us with S9’s are having this problem right now. I’m so upset. I put so much into this. What do I do now? Can’t you just send me a replacement hash board asap please?

I am seeing multiple people this month with the same problem as me, One hashing board and temps and zero’s no longer show up or works anymore. Has this problem been addressed for anyone?

Hi Edward, please submit a support ticket so that we can help you troubleshoot. Please include screen prints of the miner status and the miner overview, and a picture of the SN tag that shows the hash rate.

Yes I have submitted support tickets and I just added screenshots in the reply section of the support e mail. Can you confirm you have received it? I’m so stressed out over this right now been up all night. Please advise. Thank you.

Edward, hi.

They will not send you a new card (panel), I was told to ship the device entirely to China. You are lucky, there is a service center in the USA, but in Russia there is not. I asked to send me a fee, I will install it myself. Have refused. I can not send, one of my devices was lost and three months I can not find out what’s wrong with my device.

This is horrible news. It seems like if the other two boards are working fine then sending a replacement board would be the best option. I am still under warranty but I really do not want to send the whole machine back and pay shipping in addition to losing the mining profits and risk more damage or the miner getting lost in the mail. This sucks. I talked bitmain up a lot and referred a lot of friends and now I am really worried. I was told by support when I ordered that these machines should last for years. I’ve taken great care of it and spent all this time and money for a costly return and headache? So bummed out right now. I don’t even want the 2 L3+ I ordered. What’s the point if they break so soon and repair is so hard? Wishing I never decided to mine right now guess everyone was right.

Hi Edward, I just sent you instructions to first try resetting the miner. That sometimes fixes the issue and avoids the need to ship the machine for repair.

I tried resetting and loading the firmware you sent me and it is still the same problem. One hash board has completely disappeared from my mining status screen and is 1/3 less the hashing power. I emailed you all the screenshots you requested as well, Please help me thank you.

I really hope bitmain can do right by me for this. I have been a loyal customer. I have placed several other orders with you and spread a lot of good word about you on facebook and referred many friends. Please help me out on this I have placed much faith in you and am very nervous right now about my S9 I’ve only had it a few months.

I have new batch of L3+ and 1 of the units hashboard is not working. please send new board.

I am so upset. I have been patient and followed every step of your repair process with my S9 which is still under warranty. I created a support ticket, troubleshooted with support, was instructed to pay shipping and ship the whole miner to California for repair, which I did. I received an e mail saying repair or replacement of my broken hash board was complete and I would have my S9 back in full working condition in 3 days. I was very impressed by support and the warranty process at this point even though I had spent so much time on this and paid for shipping. Received mu miner yesterday and it is in the same exact condition. It still does NOT work and the same hash board is still broken and my S9 still only hashes at 2/3 of it’s hashing power. Why? Why would you put me through all this work and have me pay shipping and just send back the miner to me in the exact same condition? Why? I have been so polite. I have followed all your repair instructions and I am still under warranty. Why are you putting me through so much grief? I don’t understand and feel like just giving up on mining all together.

nicson1989

Свой человек

pyhtin79

Пляшущий с бубном

lasthiter

Свой человек

Попробуй сделать вот это, у меня тоже самое было, те же 400, пока я не проделал такую манипуляцию.

Включение параметра «Блокировка страниц в памяти»

-

В меню Пуск выберите команду Выполнить. В окне Открыть введите gpedit.msc.

В консоли Редактор локальных групповых политик разверните узел Конфигурация компьютера, затем узел Конфигурация Windows.

Разверните узлы Настройки безопасностии Локальные политики.

Выберите папку Назначение прав пользователя .

Политики будут показаны на панели подробностей.

На этой панели дважды щелкните параметр Блокировка страниц в памяти.

В диалоговом окне Параметр локальной безопасности — блокировка страниц в памяти щелкните Добавить пользователя или группу.

В диалоговом окне Выбор: пользователи, учетные записи служб или группы добавьте учетную запись, обладающую правами доступа для запуска sqlservr.exe.

iDekabrist

Бывалый

pyhtin79

Пляшущий с бубном

Попробуй сделать вот это, у меня тоже самое было, те же 400, пока я не проделал такую манипуляцию.

Включение параметра «Блокировка страниц в памяти»

-

В меню Пуск выберите команду Выполнить. В окне Открыть введите gpedit.msc.

В консоли Редактор локальных групповых политик разверните узел Конфигурация компьютера, затем узел Конфигурация Windows.

Разверните узлы Настройки безопасностии Локальные политики.

Выберите папку Назначение прав пользователя .

Политики будут показаны на панели подробностей.

На этой панели дважды щелкните параметр Блокировка страниц в памяти.

В диалоговом окне Параметр локальной безопасности — блокировка страниц в памяти щелкните Добавить пользователя или группу.

В диалоговом окне Выбор: пользователи, учетные записи служб или группы добавьте учетную запись, обладающую правами доступа для запуска sqlservr.exe.