|

V. Hunter Adams (vha3@cornell.edu)¶

Video discussion of the content on this page¶

Hardware Hookup¶

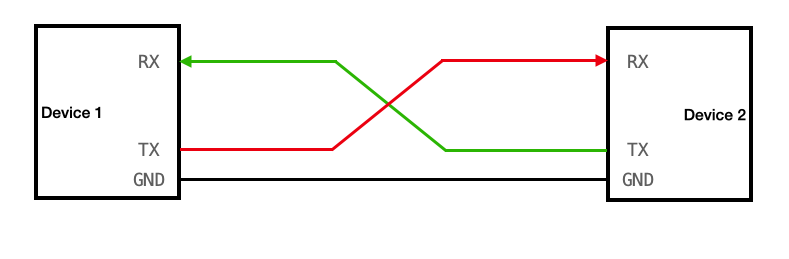

A UART channel has two data lines. On each device there is an RX pin and a TX pin (RX for receive and TX for transmit). The RX pin of each device is connected to the TX pin of the other. Note that there is no shared clock line! This is the «asynchronous» aspect of Universal Asynchronous Receiver Transmitter.

Timing Diagram¶

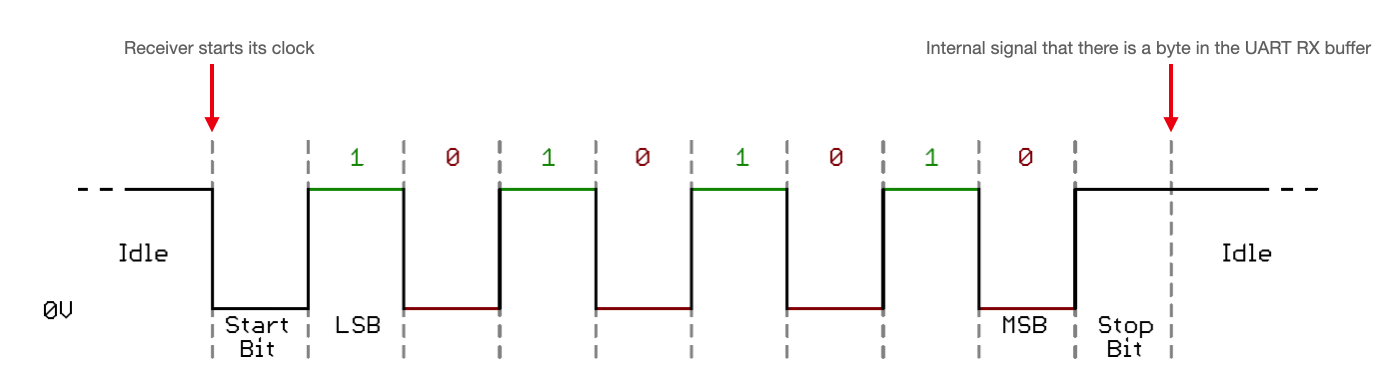

In an idle state, the Tx line from the sending device is held high. This is a legacy of old telegraph machines, for which the line is held high to make it obvious that it is not damaged. To send a packet, the transmitter first sends a start bit, which pulls the line low.

“UART” stands for Universal Asynchronous Receiver-Transmitter. The word “Asynchronous” in the name means that there is no shared clock between the transmitter and receiver. Instead, this start bit acts like a synchronization pulse between the transmitter and receiver. Each has their own clock, and they synchronize those clocks using the falling edge of this start bit.

That suggests that those two clocks need to running at the same speed. And indeed they do. These need to by synchronized to within ~2 percent or communication won’t work.

After this start bit 8 (or 9, depending on the configuration) bits are sent in least significant bit first format. At the end of the packet, there is a stop bit. The stop bit is one more down time followed by a rising edge. When the receiver sees the rising edge of that stop bit, it knows that there is now a valid character in its receive buffer and it will send some sort of internal signal to indicate as such. It may throw an interrupt, for example. It needs some sort of signal because this is asynchronous — a valid character could arrive at any time.

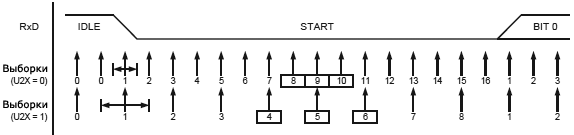

The number of clock pulses per bit can be configured to be 4 or 16. With only 4 pulses per bit, you can transmit faster, but you also only use a single sample per bit to determine whether a high or low level is present. With 16x the baud rate, majority detect circuitry is implemented to determine the value on the RX pin. The fastest that you can transmit is 1/4 the clock rate. So, at 40 MHz, you can in principle send data at up to 10Mbps, but don’t expect to be able to do that over very far distances.

Some things to notice about this protocol:

- It takes 10 bit-times to transmit 8-bits.

- It takes 1/(baud rate) seconds to transmit each bit

- The number of clock pulses per bit is configurable (4 or 16)

- You could transmit at up to 1/4 the clock rate, but not for very far distances

- Clock synchronization to within about 2 percent is required for successful communication

Error states¶

Framing errors¶

The UART status and control registers will indicate various status conditions, including error states associated with a transmission. Understanding this protocol makes understanding the error states a bit easier. They include framing errors, which occur when the receiver does not see a stop bit at the expected bit time. If the data line is not in the expected high state when the stop bit is expected (according to the number of data and parity bits for which the UART is set), the UART will signal a framing error.

Parity error¶

A parity error only gets thrown if the UART is in parity mode. In parity mode, an extra bit is sent which holds the parity (even or odd) of all of the transmitted data bits. If there is an error in a data bit (1 for 0 or 0 for 1), this parity bit will be wrong and an error will be thrown specifying an error.

Overrun error¶

An overrun error occurs when the receiver has not processed (removed characters from the input buffer) before the next character arrives.

Break condition¶

A break condition is not an error, necessarily. It occurs when the receiver input is at a logic level low state for longer than some duration of time, typically for more than a character time. It looks to the receiver like a character of all zero bits with a framing error. This is hacked for the software reset circuitry. In the python code, you can see that a reset is triggered by sending a break. This pulls the data line low for long enough that MCLR is pulled low and the board resets.

9-bit networking¶

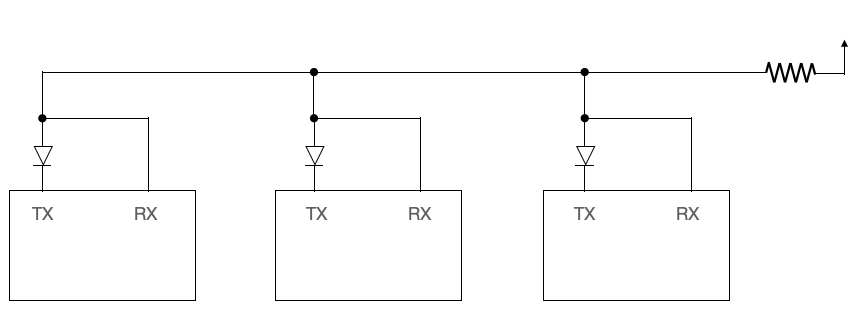

There is a configuration that allows you to setup a network that uses UART as the communication protocol. Doing so requires that all the lines of all the devices are wired together. There’s a diode going into each Tx line, and the whole thing is gently pulled up by a pull-up resistor.

This configuration means that a transmit pin can pull down the line, and the resistor will pull it back up. You then need a scheme for addressing a particular device from a particular device. A way to do this is to configure the UART to 9-bit mode (which means, as the name suggests, that 9 data bits are transmitted instead of 8). That 9th bit is then used to indicate whether the information that was just sent was an address or data.

If it was an address, then all secondary devices look for a match of their own hardcoded addresses. If they receive a match, they can be configured to automatically setup their receive/transmit functions. This address stays the bus address until a new address is sent. In other words, it’s persistent.

A universal asynchronous receiver-transmitter (UART ) is a computer hardware device for asynchronous serial communication in which the data format and transmission speeds are configurable. It sends data bits one by one, from the least significant to the most significant, framed by start and stop bits so that precise timing is handled by the communication channel. The electric signaling levels are handled by a driver circuit external to the UART. Two common signal levels are RS-232, a 12-volt system, and RS-485, a 5-volt system. Early teletypewriters used current loops.

It was one of the earliest computer communication devices, used to attach teletypewriters for an operator console. It was also an early hardware system for the Internet.

A UART is usually an individual (or part of an) integrated circuit (IC) used for serial communications over a computer or peripheral device serial port. One or more UART peripherals are commonly integrated in microcontroller chips. Specialised UARTs are used for automobiles, smart cards and SIMs.

A related device, the universal synchronous and asynchronous receiver-transmitter (USART) also supports synchronous operation.

Transmitting and receiving serial data[edit]

The universal asynchronous receiver-transmitter (UART) takes bytes of data and transmits the individual bits in a sequential fashion.[1] At the destination, a second UART re-assembles the bits into complete bytes. Each UART contains a shift register, which is the fundamental method of conversion between serial and parallel forms. Serial transmission of digital information (bits) through a single wire or other medium is less costly than parallel transmission through multiple wires.

The UART usually does not directly generate or receive the external signals used between different items of equipment. Separate interface devices are used to convert the logic level signals of the UART to and from the external signalling levels, which may be standardized voltage levels, current levels, or other signals.

Communication may be 3 modes:

- simplex (in one direction only, with no provision for the receiving device to send information back to the transmitting device)

- full duplex (both devices send and receive at the same time)

- half duplex (devices take turns transmitting and receiving)

Data framing[edit]

| 1 | 5-9 | 0-1 | 1-2 |

|---|---|---|---|

| Start Bit | Data Frame | Parity Bits | Stop Bits |

For UART to work the following settings need to be the same on both the transmitting and receiving side:

- Baud Rate

- Parity bit

- Data bits size

- Stop bits size

- Flow Control

In the most common settings of 8 data bits, no parity and 1 stop bit (aka 8N1), the protocol efficiency is 80%. Ethernet by comparison is up to 97%.

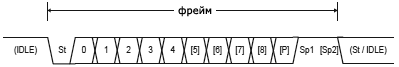

Example of a UART frame. In this diagram, one byte is sent, consisting of a start bit, followed by eight data bits (D0-7), and two stop bit, for a 11-bit UART frame. The number of data and formatting bits, the presence or absence of a parity bit, the form of parity (even or odd) and the transmission speed must be pre-agreed by the communicating parties. The «stop bit» is actually a «stop period»; the stop period of the transmitter may be arbitrarily long. It cannot be shorter than a specified amount, usually 1 to 2 bit times. The receiver requires a shorter stop period than the transmitter. At the end of each data frame, the receiver stops briefly to wait for the next start bit. It is this difference which keeps the transmitter and receiver synchronized. BCLK = Base Clock

A UART frame consists of 5 elements:

- Idle (logic high (1))

- Start bit (logic low (0))

- Data bits

- Parity bit

- Stop (logic high (1))

The idle, no data state is high-voltage, or powered. This is a historic legacy from telegraphy, in which the line is held high to show that the line and transmitter are not damaged.

Each character is framed as a logic low start bit, data bits, possibly a parity bit and one or more stop bits. In most applications the least significant data bit (the one on the left in this diagram) is transmitted first, but there are exceptions (such as the IBM 2741 printing terminal).

Start bit[edit]

The start bit signals the receiver that a new character is coming.

Data bit[edit]

The next five to nine bits, depending on the code set employed, represent the character.

Parity bit[edit]

If a parity bit is used, it would be placed after all of the data bits.

It describes the odd or eveness of the number.

Stop bit[edit]

The next one or two bits are always in the mark (logic high, i.e., ‘1’) condition and called the stop bit(s). They signal to the receiver that the character is complete. Since the start bit is logic low (0) and the stop bit is logic high (1) there are always at least two guaranteed signal changes between characters.

If the line is held in the logic low condition for longer than a character time, this is a break condition that can be detected by the UART.

Receiver[edit]

All operations of the UART hardware are controlled by an internal clock signal which runs at a multiple of the data rate, typically 8 or 16 times the bit rate. The receiver tests the state of the incoming signal on each clock pulse, looking for the beginning of the start bit. If the apparent start bit lasts at least one-half of the bit time, it is valid and signals the start of a new character. If not, it is considered a spurious pulse and is ignored. After waiting a further bit time, the state of the line is again sampled and the resulting level clocked into a shift register. After the required number of bit periods for the character length (5 to 8 bits, typically) have elapsed, the contents of the shift register are made available (in parallel fashion) to the receiving system. The UART will set a flag indicating new data is available, and may also generate a processor interrupt to request that the host processor transfers the received data.

Communicating UARTs have no shared timing system apart from the communication signal. Typically, UARTs resynchronize their internal clocks on each change of the data line that is not considered a spurious pulse. Obtaining timing information in this manner, they reliably receive when the transmitter is sending at a slightly different speed than it should. Simplistic UARTs do not do this; instead they resynchronize on the falling edge of the start bit only, and then read the center of each expected data bit, and this system works if the broadcast data rate is accurate enough to allow the stop bits to be sampled reliably.[2][3]

It is a standard feature for a UART to store the most recent character while receiving the next. This «double buffering» gives a receiving computer an entire character transmission time to fetch a received character. Many UARTs have a small first-in, first-out (FIFO) buffer memory between the receiver shift register and the host system interface. This allows the host processor even more time to handle an interrupt from the UART and prevents loss of received data at high rates.

Transmitter[edit]

Transmission operation is simpler as the timing does not have to be determined from the line state, nor is it bound to any fixed timing intervals. As soon as the sending system deposits a character in the shift register (after completion of the previous character), the UART generates a start bit, shifts the required number of data bits out to the line, generates and sends the parity bit (if used), and sends the stop bits. Since full-duplex operation requires characters to be sent and received at the same time, UARTs use two different shift registers for transmitted and received characters. High performance UARTs could contain a transmit FIFO (first in first out) buffer to allow a CPU or DMA controller to deposit multiple characters in a burst into the FIFO rather than have to deposit one character at a time into the shift register. Since transmission of a single or multiple characters may take a long time relative to CPU speeds, a UART maintains a flag showing busy status so that the host system knows if there is at least one character in the transmit buffer or shift register; «ready for next character(s)» may also be signaled with an interrupt.

Application[edit]

Transmitting and receiving UARTs must be set for the same bit speed, character length, parity, and stop bits for proper operation. The receiving UART may detect some mismatched settings and set a «framing error» flag bit for the host system; in exceptional cases, the receiving UART will produce an erratic stream of mutilated characters and transfer them to the host system.

Typical serial ports used with personal computers connected to modems use eight data bits, no parity, and one stop bit; for this configuration, the number of ASCII characters per second equals the bit rate divided by 10.

Some very low-cost home computers or embedded systems dispense with a UART and use the CPU to sample the state of an input port or directly manipulate an output port for data transmission. While very CPU-intensive (since the CPU timing is critical), the UART chip can thus be omitted, saving money and space. The technique is known as bit-banging.

History[edit]

Some early telegraph schemes used variable-length pulses (as in Morse code) and rotating clockwork mechanisms to transmit alphabetic characters. The first serial communication devices (with fixed-length pulses) were rotating mechanical switches (commutators). Various character codes using 5, 6, 7, or 8 data bits became common in teleprinters and later as computer peripherals. The teletypewriter made an excellent general-purpose I/O device for a small computer.

Gordon Bell of DEC designed the first UART, occupying an entire circuit board called a line unit, for the PDP series of computers beginning with the PDP-1.[4][5]

According to Bell, the main innovation of the UART was its use of sampling to convert the signal into the digital domain, allowing more reliable timing than previous circuits that used analog timing devices with manually adjusted potentiometers.[6] To reduce the cost of wiring, backplane and other components, these computers also pioneered flow control using XON and XOFF characters rather than hardware wires.

DEC condensed the line unit design into an early single-chip UART for their own use.[4] Western Digital developed this into the first widely available single-chip UART, the WD1402A, around 1971. This was an early example of a medium-scale integrated circuit. Another popular chip was the SCN2651 from the Signetics 2650 family.

An example of an early 1980s UART was the National Semiconductor 8250 used in the original IBM PC’s Asynchronous Communications Adapter card.[7] In the 1990s, newer UARTs were developed with on-chip buffers. This allowed higher transmission speed without data loss and without requiring such frequent attention from the computer. For example, the popular National Semiconductor 16550 has a 16-byte FIFO, and spawned many variants, including the 16C550, 16C650, 16C750, and 16C850.

Depending on the manufacturer, different terms are used to identify devices that perform the UART functions. Intel called their 8251 device a «Programmable Communication Interface». MOS Technology 6551 was known under the name «Asynchronous Communications Interface Adapter» (ACIA). The term «Serial Communications Interface» (SCI) was first used at Motorola around 1975 to refer to their start-stop asynchronous serial interface device, which others were calling a UART. Zilog manufactured a number of Serial Communication Controllers or SCCs.

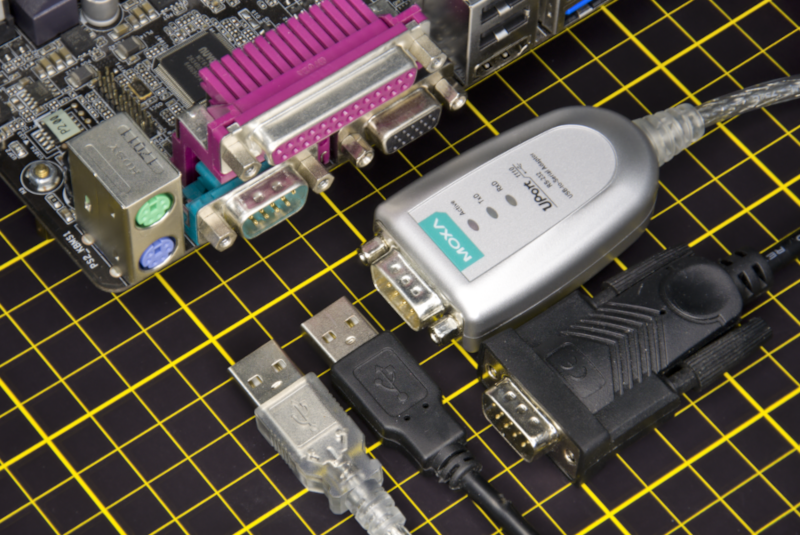

Starting in the 2000s, most IBM PC compatible computers removed their external RS-232 COM ports and used USB ports that can send data faster. For users who still need RS-232 serial ports, external USB-to-UART bridges are now commonly used. They combine the hardware cables and a chip to do the USB and UART conversion. Cypress Semiconductor and FTDI are two of the significant commercial suppliers of these chips.[8] Although RS-232 ports are no longer available to users on the outside of most computers, many internal processors and microprocessors have UARTs built into their chips to give hardware designers the ability to interface with other chips or devices that use RS-232 or RS-485 for communication.

Structure[edit]

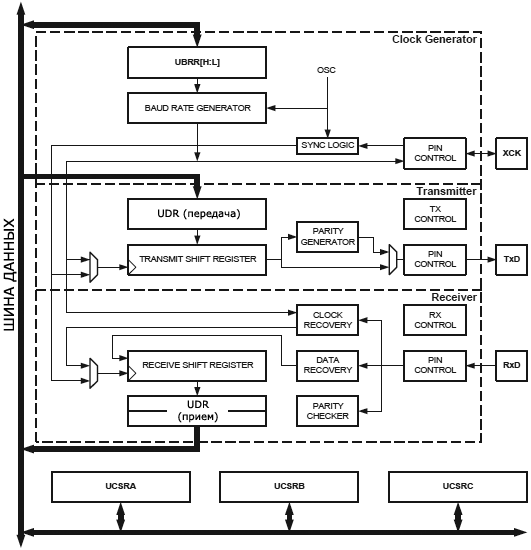

A UART usually contains the following components:

- a clock generator, usually a multiple of the bit rate to allow sampling in the middle of a bit period

- input and output shift registers

- transmit/receive control

- read/write control logic

- autobaud measurement (optional)

- transmit/receive buffers (optional)

- system data bus buffer (optional)

- first-in, first-out (FIFO) buffer memory (optional)

- signals needed by a third party DMA controller (optional)

- integrated bus mastering DMA controller (optional)

Special transceiver conditions[edit]

Overrun error[edit]

An overrun error occurs when the receiver cannot process the character that just came in before the next one arrives. Various devices have different amounts of buffer space to hold received characters. The CPU or DMA controller must service the UART in order to remove characters from the input buffer. If the CPU or DMA controller does not service the UART quickly enough and the buffer becomes full, an overrun error will occur, and incoming characters will be lost.

Underrun error[edit]

An underrun error occurs when the UART transmitter has completed sending a character and the transmit buffer is empty. In asynchronous modes this is treated as an indication that no data remains to be transmitted, rather than an error, since additional stop bits can be appended. This error indication is commonly found in USARTs, since an underrun is more serious in synchronous systems.

Framing error[edit]

A UART will detect a framing error when it does not see a «stop» bit at the expected «stop» bit time. As the «start» bit is used to identify the beginning of an incoming character, its timing is a reference for the remaining bits. If the data line is not in the expected state (high) when the «stop» bit is expected (according to the number of data and parity bits for which the UART is set), the UART will signal a framing error. A «break» condition on the line is also signaled as a framing error.

Parity error[edit]

A parity error occurs when the parity of the number of one-bits disagrees with that specified by the parity bit. Parity checking is often used for the detection of transmission errors. Use of a parity bit is optional, so this error will only occur if parity-checking has been enabled.

Break condition[edit]

A break condition occurs when the receiver input is at the «space» (logic low, i.e., ‘0’) level for longer than some duration of time, typically, for more than a character time. This is not necessarily an error, but appears to the receiver as a character of all zero-bits with a framing error.

The term «break» derives from current loop signaling, which was the traditional signaling used for teletypewriters. The «spacing» condition of a current loop line is indicated by no current flowing, and a very long period of no current flowing is often caused by a break or other fault in the line. Some equipment will deliberately transmit the «space» level for longer than a character as an attention signal. When signaling rates are mismatched, no meaningful characters can be sent, but a long «break» signal can be a useful way to get the attention of a mismatched receiver to do something (such as resetting itself). Computer systems can use the long «break» level as a request to change the signaling rate, to support dial-in access at multiple signaling rates. The DMX512 protocol uses the break condition to signal the start of a new packet.

UART models[edit]

A dual UART, or DUART, combines two UARTs into a single chip. Similarly, a quadruple UART or QUART, combines four UARTs into one package, such as the NXP 28L194. An octal UART or OCTART combines eight UARTs into one package, such as the Exar XR16L788 or the NXP SCC2698.

| Model | Description |

|---|---|

| WD1402A | The first single-chip UART on general sale. Introduced about 1971. Compatible chips included the Fairchild TR1402A and the General Instruments AY-5-1013.[9] |

| Exar XR21V1410 | |

| Intersil 6402 | |

| CDP 1854 (RCA, now Intersil) | |

| Zilog Z8440 | Universal synchronous and asynchronous receiver-transmitter. 2000 kbit/s. Async, Bisync, SDLC, HDLC, X.25. CRC. 4-byte RX buffer. 2-byte TX buffer. Provides signals needed by a third party DMA controller to perform DMA transfers.[10] |

| Z8530/Z85C30 | This universal synchronous and asynchronous receiver-transmitter has a 3-byte receive buffer and a 1-byte transmit buffer. It has hardware to accelerate the processing of HDLC and SDLC. The CMOS version (Z85C30) provides signals to allow a third party DMA controller to perform DMA transfers. It can do asynchronous, byte level synchronous, and bit level synchronous communications.[11] |

| 8250 | Obsolete with 1-byte buffers. These UARTs’ maximum standard serial port speed is 9600 bits per second if the operating system has a 1 millisecond interrupt latency. 8250 UARTs were used in the IBM PC 5150 and IBM PC/XT, while the 16450 UART were used in IBM PC/AT-series computers. |

| 8251 | |

| Motorola 6850 | |

| 6551 | |

| Rockwell 65C52 | |

| 16450 | |

| 82510 | This UART allows asynchronous operation up to 288 kbit/s, with two independent four-byte FIFOs. It was produced by Intel at least from 1993 to 1996, and Innovastic Semiconductor has a 2011 Data Sheet for IA82510. |

| 16550 | This UART’s FIFO is broken, so it cannot safely run any faster than the 16450 UART. The 16550A and later versions fix this bug. |

| 16550A | This UART has 16-byte FIFO buffers. Its receive interrupt trigger levels can be set to 1, 4, 8, or 14 characters. Its maximum standard serial port speed if the operating system has a 1 millisecond interrupt latency is 128 kbit/s. Systems with lower interrupt latencies or with DMA controllers could handle higher baud rates. This chip can provide signals that are needed to allow a DMA controller to perform DMA transfers to and from the UART if the DMA mode this UART introduces is enabled.[12] It was introduced by National Semiconductor, which has been sold to Texas Instruments. National Semiconductor claimed that this UART could run at up to 1.5 Mbit/s. |

| 16C552 | |

| 16650 | This UART was introduced by Startech Semiconductor which is now owned by Exar Corporation and is not related to Startech.com. Early versions have a broken FIFO buffer and therefore cannot safely run any faster than the 16450 UART.[13] Versions of this UART that were not broken have 32-character FIFO buffers and could function at standard serial port speeds up to 230.4 kbit/s if the operating system has a 1 millisecond interrupt latency. Current versions of this UART by Exar claim to be able to handle up to 1.5 Mbit/s. This UART introduces the Auto-RTS and Auto-CTS features in which the RTS# signal is controlled by the UART to signal the external device to stop transmitting when the UART’s buffer is full to or beyond a user-set trigger point and to stop transmitting to the device when the device drives the CTS# signal high (logic 0). |

| 16750 | 64-byte buffers. This UART can handle a maximum standard serial port speed of 460.8 kbit/s if the maximum interrupt latency is 1 millisecond. This UART was introduced by Texas Instruments. TI claims that early models can run up to 1 Mbit/s, and later models in this series can run up to 3 Mbit/s. |

| 16850 | 128-byte buffers. This UART can handle a maximum standard serial port speed of 921.6 kbit/s if the maximum interrupt latency is 1 millisecond. This UART was introduced by Exar Corporation. Exar claims that early versions can run up to 2 Mbit/s, and later versions can run up to 2.25 Mbit/s depending on the date of manufacture. |

| 16C850 | |

| 16950 | 128-byte buffers. This UART can handle a maximum standard serial port speed of 921.6 kbit/s if the maximum interrupt latency is 1 millisecond. This UART supports 9-bit characters in addition to the 5- to 8-bit characters that other UARTs support. This was introduced by Oxford Semiconductor, which is now owned by PLX Technology. Oxford/PLX claims that this UART can run up to 15 Mbit/s. PCI Express variants by Oxford/PLX are integrated with a first party bus mastering PCIe DMA controller. This DMA controller uses the UART’s DMA mode signals that were defined for the 16550. The DMA controller requires the CPU to set up each transaction and poll a status register after the transaction is started to determine if the transaction is done. Each DMA transaction can transfer between 1 and 128 bytes between a memory buffer and the UART. PCI Express variants can also allow the CPU to transfer data between itself and the UART with 8-, 16-, or 32-bit transfers when using programmed I/O. |

| 16C950 | |

| 16954 | Quad-port version of the 16950/16C950. 128-byte buffers. This UART can handle a maximum standard serial port speed of 921.6 kbit/s if the maximum interrupt latency is 1 millisecond. This UART supports 9-bit characters in addition to the 5–8 bit characters that other UARTs support. This was introduced by Oxford Semiconductor, which is now owned by PLX Technology. Oxford/PLX claims that this UART can run up to 15 Mbit/s. PCI Express variants by Oxford/PLX are integrated with a first party bus mastering PCIe DMA controller. This DMA controller is controlled by the UART’s DMA mode signals that were defined for the 16550. The DMA controller requires the CPU to set up each transaction and poll a status register after the transaction is started to determine if the transaction is done. Each DMA transaction can transfer between 1 and 128 bytes between a memory buffer and the UART. PCI Express variants can also allow the CPU to transfer data between itself and the UART with 8-, 16-, or 32-bit transfers when using programmed I/O. |

| 16C954 | |

| 16C1550/16C1551 | UART with 16-byte FIFO buffers. Up to 1.5 Mbit/s. The ST16C155X is not compatible with the industry standard 16550 and will not work with the standard serial port driver in Microsoft Windows. |

| 16C2450 | Dual UART with 1-byte FIFO buffers. |

| 16C2550 | Dual UART with 16-byte FIFO buffers. Pin-to-pin and functional compatible to 16C2450. Software compatible with INS8250 and NS16C550. |

| SCC2691 | Currently produced by NXP, the 2691[3] is a single channel UART that also includes a programmable counter/timer. The 2691 has a single-byte transmitter holding register and a 4-byte receive FIFO. Maximum standard speed of the 2692 is 115.2 kbit/s.

The 28L91 is an upwardly compatible version of the 2691, featuring selectable 8- or 16-byte transmitter and receiver FIFOs, improved support for extended data rates, and faster bus timing characteristics, making the device more suitable for use with high performance microprocessors. Both the 2691 and 28L91 may also be operated in TIA-422 and TIA-485 modes, and may also be programmed to support non-standard data rates. The devices are produced in PDIP-40, PLCC-44 and 44 pin QFP packages, and are readily adaptable to both Motorola and Intel buses. They have also been successfully adapted to the 65C02 and 65C816 buses. The 28L91 will operate on 3.3 or 5 volts. |

| SCC28L91 | |

| SCC2692 | Currently produced by NXP, these devices are dual UARTs (DUART), consisting of two communications channels, associated control registers and one counter/timer. Each communication channel is independently programmable and supports independent transmit and receive data rates.

The 2692 has a single-byte transmitter holding register and a 4-byte receiver FIFO for each channel. Maximum standard speed of both of the 2692’s channels is 115.2 kbit/s. The 26C92 is an upwardly compatible version of the 2692, with 8-byte transmitter and receiver FIFOs for improved performance during continuous bi-directional asynchronous transmission (CBAT) on both channels at the maximum standard speed of 230.4 kbit/s. The letter C in the 26C92 part number has nothing to do with the fabrication process; all NXP UARTs are CMOS devices. The 28L92 is an upwardly compatible version of the 26C92, featuring selectable 8- or 16-byte transmitter and receiver FIFOs, improved support for extended data rates, and faster bus timing characteristics, making the device more suitable for use with high performance microprocessors. The 2692, 26C92 and 28L92 may be operated in TIA-422 and TIA-485 modes, and may also be programmed to support non-standard data rates. The devices are produced in PDIP-40, PLCC-44 and 44 pin QFP packages, and are readily adaptable to both Motorola and Intel buses. They have also been successfully adapted to the 65C02 and 65C816 buses. The 28L92 will operate on 3.3 or 5 volts. |

| SC26C92 | |

| SC28L92 | |

| SCC28C94 | Currently produced by NXP, the 28C94 quadruple UART (QUART) is functionally similar to a pair of SCC26C92 DUARTs mounted in a common package, with the addition of an arbitrated interrupt system for efficient processing during periods of intense channel activity. Some additional signals are present to support the interrupt management features and the auxiliary input/output pins are arranged differently than those of the 26C92. Otherwise, the programming model for the 28C94 is similar to that of the 26C92, requiring only minor code changes to fully utilize all features. The 28C94 supports a maximum standard speed of 230.4 kbit/s, is available in a PLCC-52 package, and is readily adaptable to both Motorola and Intel buses. It has also been successfully adapted to the 65C816 bus. |

| SCC2698B | Currently produced by NXP, the 2698 octal UART (OCTART) is essentially four SCC2692 DUARTs in a single package. Specifications are the same as the SCC2692 (not the SCC26C92). Due to the lack of transmitter FIFOs and the small size of the receiver FIFOs, the 2698 can cause an interrupt «storm» if all channels are simultaneously engaged in continuous bi-directional communication. The device is produced in PDIP-64 and PLCC-84 packages, and is readily adaptable to both Motorola and Intel buses. The 2698 has also been successfully adapted to the 65C02 and 65C816 buses. |

| SCC28L198 | Currently produced by NXP, the 28L198 OCTART is essentially an upscaled enhancement of the SCC28C94 QUART described above, with eight independent communications channels, as well as an arbitrated interrupt system for efficient processing during periods of intense channel activity. The 28L198 supports a maximum standard speed of 460.8 kbit/s, is available in PLCC-84 and LQFP-100 packages, and is readily adaptable to both Motorola and Intel buses. The 28L198 will operate on 3.3 or 5 volts. |

| Z85230 | Synchronous/Asynchronous modes, 2 ports. Provides signals needed by a third party DMA controller needed to perform DMA transfers. 4-byte buffer to send, 8-byte buffer to receive per channel. SDLC/HDLC modes. 5 Mbit/s in synchronous mode. |

| Hayes ESP | 1 KB buffers, 921.6 kbit/s, 8-ports.[14] |

| Exar XR17V352, XR17V354 and XR17V358 | Dual, Quad and Octal PCI Express UARTs with 16550 compatible register Set, 256-byte TX and RX FIFOs, Programmable TX and RX Trigger Levels, TX/RX FIFO Level Counters, Fractional baud rate generator, Automatic RTS/CTS or DTR/DSR hardware flow control with programmable hysteresis, Automatic Xon/Xoff software flow control, RS-485 half duplex direction control output with programmable turn-around delay, Multi-drop with Auto Address Detection, Infrared (IrDA 1.1) data encoder/decoder. They are specified up to 25 Mbit/s. DataSheets are dated from 2012. |

| Exar XR17D152, XR17D154 and XR17D158 | Dual, Quad and Octal PCI bus UARTs with 16C550 Compatible 5G Register Set, 64-byte Transmit and Receive FIFOs, Transmit and Receive FIFO Level Counters, Programmable TX and RX FIFO Trigger Level, Automatic RTS/CTS or DTR/DSR Flow Control, Automatic Xon/Xoff Software Flow Control, RS485 HDX Control Output with Selectable Turn-around Delay, Infrared (IrDA 1.0) Data Encoder/Decoder, Programmable Data Rate with Prescaler, Up to 6.25 Mbit/s Serial Data Rate. DataSheets are dated from 2004 and 2005. |

| Exar XR17C152, XR17C154 and XR17C158 | Dual, Quad and Octal 5 V PCI bus UARTs with 16C550 Compatible Registers, 64-byte Transmit and Receive FIFOs, Transmit and Receive FIFO Level Counters, Automatic RTS/CTS or DTR/DSR Flow Control, Automatic Xon/Xoff Software Flow Control, RS485 Half-duplex Control with Selectable Delay, Infrared (IrDA 1.0) Data Encoder/Decoder, Programmable Data Rate with Prescaler, Up to 6.25 Mbit/s Serial Data Rate. DataSheets are dated from 2004 and 2005. |

| Exar XR17V252, XR17V254 and XR17V258 | Dual, Quad and Octal 66 MHz PCI bus UARTs with Power Management Support, 16C550 compatible register set, 64-byte TX and RX FIFOs with level counters and programmable trigger levels, Fractional baud rate generator, Automatic RTS/CTS or DTR/DSR hardware flow control with programmable hysteresis, Automatic Xon/Xoff software flow control, RS-485 half duplex direction control output with selectable turn-around delay, Infrared (IrDA 1.0) data encoder/decoder, Programmable data rate with prescaler. DataSheets are dated from 2008 and 2010. |

UART in modems[edit]

Modems for personal computers that plug into a motherboard slot must also include the UART function on the card. The original 8250 UART chip shipped with the IBM personal computer had a one character buffer for the receiver and the transmitter each, which meant that communications software performed poorly at speeds above 9600 bit/s, especially if operating under a multitasking system or if handling interrupts from disk controllers. High-speed modems used UARTs that were compatible with the original chip but which included additional FIFO buffers, giving software additional time to respond to incoming data.

A look at the performance requirements at high bit rates shows why the 16-, 32-, 64- or 128-byte FIFO is a necessity. The Microsoft specification for a DOS system requires that interrupts not be disabled for more than 1 millisecond at a time. Some hard disk drives and video controllers violate this specification. 9600 bit/s will deliver a character approximately every millisecond, so a 1-byte FIFO should be sufficient at this rate on a DOS system which meets the maximum interrupt disable timing. Rates above this may receive a new character before the old one has been fetched, and thus the old character will be lost. This is referred to as an overrun error and results in one or more lost characters.

A 16-byte FIFO allows up to 16 characters to be received before the computer has to service the interrupt. This increases the maximum bit rate the computer can process reliably from 9600 to 153,000 bit/s if it has a 1 millisecond interrupt dead time. A 32-byte FIFO increases the maximum rate to over 300,000 bit/s. A second benefit to having a FIFO is that the computer only has to service about 8 to 12% as many interrupts, allowing more CPU time for updating the screen, or doing other chores. Thus the computer’s responses will improve as well.

See also[edit]

- Automatic baud rate detection

- Baud

- Bit rate

- Comparison of synchronous and asynchronous signalling

- Crystal oscillator frequencies

- MIDI

- Synchronous serial communication

References[edit]

- ^ Adam Osborne, An Introduction to Microcomputers Volume 1: Basic Concepts, Osborne-McGraw Hill Berkeley California USA, 1980 ISBN 0-931988-34-9 pp. 116–126

- ^ «Determining Clock Accuracy Requirements for UART Communications» (PDF). an2141. Maxim Integrated. 2003-08-07. Retrieved 1 November 2021.

- ^ a b «Universal asynchronous receiver/transmitter (UART)» (PDF). SCC2691. Philips NXP. 2006-08-04. p. 14. Retrieved 1 November 2021.

{{cite web}}: CS1 maint: url-status (link) - ^ a b C. Gordon Bell, J. Craig Mudge, John E. McNamara, Computer Engineering: A DEC View of Hardware Systems Design, Digital Press, 12 May 2014, ISBN 1483221105, p. 73

- ^ Allison, David. «Curator, Division of Information Technology and Society, National Museum of American History, Smithsonian Institution». Smithsonian Institution Oral and Video Histories. Retrieved 14 June 2015.

- ^ Oral History of Gordon Bell, 2005, accessed 2015-08-19

- ^ Technical Reference 6025008 (PDF). Personal Computer Hardware Reference Library. IBM. August 1981. pp. 2–123.

- ^ «FTDI Products». www.ftdichip.com. Retrieved 22 March 2018.

- ^ Interfacing with a PDP-11/05: the UART, blinkenbone.com, accessed 2015-08-19

- ^ «Zilog Product specification Z8440/1/2/4, Z84C40/1/2/3/4. Serial input/output controller» (PDF). 090529 zilog.com

- ^ «Zilog Document Download» (PDF). www.zilog.com. Retrieved 22 March 2018.

- ^ «FAQ: The 16550A UART & TurboCom drivers 1994». Retrieved January 16, 2016.

- ^ T’so, Theodore Y. (January 23, 1999). «Re: Serial communication with the 16650». The Mail Archive. Retrieved June 2, 2013.

- ^ bill.herrin.us — Hayes ESP 8-port Enhanced Serial Port Manual, 2004-03-02

Further reading[edit]

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded Systems; 2nd Edition; Jan Axelson; Lakeview Research; 380 pages; 2007; ISBN 978-1-931-44806-2.

- Serial Port Complete: Programming and Circuits for RS-232 and RS-485 Links and Networks; 1st Edition; Jan Axelson; Lakeview Research; 306 pages; 1998; ISBN 978-0-965-08192-4.

- Serial port and Microcontrollers: Principles, Circuits, and Source Codes; 1st Edition; Grzegorz Niemirowski; CreateSpace; 414 pages; 2013; ISBN 978-1-481-90897-9.

- Serial Programming (Wikibook).

External links[edit]

- FreeBSD Serial and UART Tutorial, includes standard signal definitions, history of UART ICs, and pinout for commonly used DB25 connector.

- UART Tutorial for Robotics, contains many practical examples.

JanJansen

Super Member

- Total Posts : 530

- Reward points : 0

- Joined: 2012/08/25 03:26:34

- Location: 0

- Status: offline

Hi, i am getting framing errors with serial communication ( for MIDI ).

Why do i get a frame error ?, because of a unexpected stop bit says the manual.

It all works good, only i keep repeated framing errors.

Someone told me that my interrupt takes to long, that might cause the framing error,

can anyone explain to me why ?

thanks in advance

jtemples

عُضْوٌ جَدِيد

- Total Posts : 12049

- Reward points : 0

- Joined: 2004/02/13 12:31:19

- Location: Southern California

- Status: offline

Re: Understanding why framing error (EUSART)

2015/03/07 11:15:48

(permalink)

Framing errors are usually caused by a baud rate mismatch between the UART and the received data.

Someone told me that my interrupt takes to long, that might cause the framing error

That is not correct. If you fail to read the UART quickly enough, that can cause an overrun error, but not a framing error.

ric

Super Member

- Total Posts : 35935

- Reward points : 0

- Joined: 2003/11/07 12:41:26

- Location: Australia, Melbourne

- Status: online

Re: Understanding why framing error (EUSART)

2015/03/07 15:17:16

(permalink)

I agree with everything jtemples just said.

JanJansen

Why do i get a frame error ?, because of a unexpected stop bit says the manual.

That is precisely the reason. A «framing error» means that the USART saw a low when it was expecting a high (in the middle of the STOP bit pulse).

This means one of:

[1] Your baud rate at sender and receiver are very different, so the receiver (i.e. the PIC) is sampling each bit earlier and earlier, so it sometimes sees the end of the 8th bit instead of the middle of the stop bit.

[2] Your sender is sending 9 bits of data, not 8. This could be if it is set to send 8 data bits + a parity bit.

[3] You have a lot of noise on the signal.

I also post at: PicForum

To get a useful answer, always state which PIC you are using!

JanJansen

Super Member

- Total Posts : 530

- Reward points : 0

- Joined: 2012/08/25 03:26:34

- Location: 0

- Status: offline

Re: Understanding why framing error (EUSART)

2015/03/08 07:50:30

(permalink)

Thanks,

only i dont understand why :

1 start bit is correct, 3 x 8 bit data is correct,

why would a stop bit be incorrect ?

DarioG

Allmächtig.

- Total Posts : 54081

- Reward points : 0

- Joined: 2006/02/25 08:58:22

- Location: Oesterreich

- Status: offline

Re: Understanding why framing error (EUSART)

2015/03/08 09:29:57

(permalink)

What are «3×8 bit data»? No start/stop in between??

JanJansen

Super Member

- Total Posts : 530

- Reward points : 0

- Joined: 2012/08/25 03:26:34

- Location: 0

- Status: offline

Re: Understanding why framing error (EUSART)

2015/03/08 09:34:54

(permalink)

1and0

Access is Denied

- Total Posts : 15919

- Reward points : 0

- Joined: 2007/05/06 12:03:20

- Location: Harry’s Gray Matter

- Status: offline

Re: Understanding why framing error (EUSART)

2015/03/08 09:59:42

(permalink)

JanJansen

only i dont understand why :

1 start bit is correct, 3 x 8 bit data is correct,

why would a stop bit be incorrect ?

Each UART frame consists of 1 start bit, 8 or 9 data bits, and 1 stop bit.

Можно с уверенностью сказать, что с момента публикации первой версии стандарта RS‑232 в мае 1960 года и по настоящее время, было написано приблизительно 109 независимых реализаций UART на всём, чём угодно. Однако, подобно «Hello world» в мире прикладного ПО, а также мигания светодиодом — «Hello world» в мире цифровой электроники (сигнализирующий об успешной настройке оборудования и среды разработки) — процесс написания UART способен проиллюстрировать особенности языка или платформы, демонстрируя применение тех или иных синтаксических конструкций для решения практических, насущных и понятных проблем.

В данном цикле статей будет рассказано про написание модуля UART на SystemVerilog, про синтез данного модуля на различных платформах и про некоторые другие аспекты применения UART в ПЛИС. Но прежде, чем писать код, поговорим про сам протокол и про особенности аппаратной части вне контекста ПЛИС.

RS-232

Представим, что у нас есть необходимость передавать данные в одну сторону по одному проводу при помощи логических уровней напряжения. Мы можем просто пустить поток бит, договорившись об одинаковой скорости передачи и приёма данных. Но принимающее устройство не будет знать, где этот поток начался, где он закончится, идёт ли он вообще, как биты распределены по байтам и так далее.

Для начала, нам потребуется заранее оговоренное состояние, которое будет считаться отсутствием передачи данных, то есть паузами между отдельными байтами. Допустим, это будет логическая единица.

Правда, без дополнительных условий будет невозможно отправить байт, состоящий из одних единиц, либо отличить последовательность 11010100 от 01010011.

Можно условиться, что к каждому передаваемому байту мы припишем дополнительный служебный бит (старт-бит), заведомо содержащий логический ноль. Тогда после паузы в передаче данных, приёмник при получении нисходящего фронта будет готов к приёму оговоренного количества бит, содержащих осмысленные данные.

Остаётся проблема: что, если будет передаваться длинная последовательность бит, содержащих нулевые значения без пауз между отдельными байтами? Тогда, рано или поздно, накопленная рассинхронизация тактовых генераторов источника и приёмника превысит половину длительности одного бита. И приёмник либо дважды прочитает один и тот же передаваемый бит, либо наоборот, пропустит один из передаваемых битов.

Нисходящий фронт старт-бита мог бы позволить синхронизироваться источнику и приёмнику каждый раз при начале передачи очередного символа, обнуляя накопившееся рассогласование. Но это возможно, только если перед старт-битом линия каждый раз будет оказываться в состоянии логической единицы. То есть если между байтами имеются хоть небольшие, но паузы. Такие обязательные паузы называются стоп-биты.

Договорившись о наличии старт-бита, стоп-битов, количестве битов данных в рамках одной передачи («символа» в терминологии UART) от старт-бита до стоп-бита и частоте следования бит можно организовать устойчивую однонаправленную передачу данных по одному проводу.

Стандарт RS-232 задаёт значение выходного напряжения логической единицы от −5 до −15 В, а логического нуля — от +5 до +15 В (именно в таком порядке). Данные уровни напряжения не поддерживаются микросхемами ПЛИС напрямую и существует несколько вариантов соединения ПЛИС с компьютером через RS‑232.

Если у компьютера предусмотрен com-порт, то соединение возможно при помощи пассивного кабеля и транслятора уровней. Зачастую трансляторы уровней для RS‑232 (к примеру, ADM3232E) изготавливают с встроенным умножителем (удвоителем) напряжения на основе переключаемых конденсаторов. Он преобразует +3,3 В в приблизительно ±6,6 В, которые используются в качестве уровней выходного сигнала на линии TX. А вход RX делают устойчивым к напряжениям вплоть до ±15 В.

Если у компьютера отсутствует встроенный com-порт, то соединение возможно при помощи внешнего преобразователя USB-RS232 (к примеру, UPort1150).

В этом случае иногда происходит некоторая путаница с разъёмами. Если разъём DB-9 на материнской плате — всегда «папа» (штыри), то разъём на оборудовании почти всегда «папа». Исключение — прецизионные источники питания компании Keithley (которую купил Tektronix). У них разъём «мама» (гнёзда). Разъём же на преобразователях USB-RS232 почти всегда, как и на материнских платах — «папа». Соответственно, он может быть подключен к Keithley непосредственно. Но для большинства оборудования дополнительно потребуется кабель «мама-мама». Разъём DB-9 предусматривает наличие стягивающих винтов. И ввиду того, что их не расположить внутри корпуса оборудования, то ими оснащается именно кабель. А на разъёмах оборудования делают гайки, куда эти винты закручиваются.

И, казалось бы, если на преобразователях USB-RS232 стоит разъём «папа» (для соединения с «мамой» кабеля, оснащённого винтами), то на нём должны быть гайки. Однако, данный элемент с вероятностью 50/50 будет также винтом! Зато к Keithley подходит идеально

-

на разъём в оборудовании и преобразователе (штыри/гнёзда)

-

на крепления в оборудовании и преобразователе (винты/гайки)

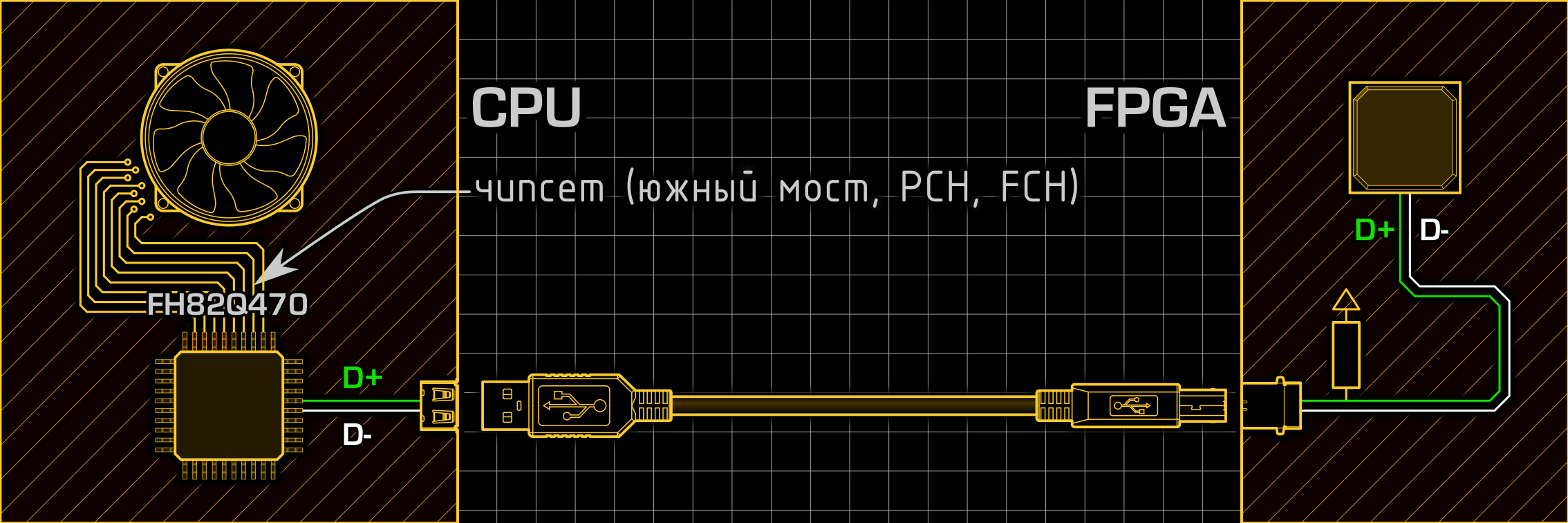

Электронная промышленность предоставляет широкую номенклатуру мостов USB-UART. Благодаря им, при создании устройства можно использовать все аппаратные плюсы интерфейса USB и при этом сохранить относительную простоту программного обеспечения, характерную для RS-232. В дальнейшем мы будем рассматривать именно этот вариант соединения, хотя с точки зрения кода для ПЛИС, разницы между предыдущими тремя примерами нет.

Есть, правда, весьма важный момент. Сам стандарт TIA/EIA-232-F (RS-232) содержит лишь электрические характеристики и размеры разъёмов. Типичные же скорости передачи данных, количество бит данных в символе, а также наличие/отсутствие дополнительного бита контрольной суммы (бита чётности) этим стандартом не оговаривается. Иногда можно встретить утверждение, что перечисленные выше аспекты оговорены в UART («Universal Asyncronous Receiver-Transmitter»), но это общее название некоторого свода обычаев передачи данных. Этому своду не соответствует какой-либо один-единственный написанный и утверждённый стандарт.

Неким подобием стандарта может считаться структура DCB, применяемая в функции SetCommState в Windows API и предназначенная для инициализации com-порта.

Так, в описании данной структуры говорится, что в символе UART может быть 1/1,5/2 стоп-бита. Однако, стандарт «ISO/IEC 7816-3», похожий на «обычный» UART и регламентирующий обмен данными со смарт-картами, предусматривает наличие 0,5 стоп-бита. И, к примеру, микроконтроллер STM32F103 способен через конфигурационные биты «STOP» ([13:12]) регистра «USART_CR2» задать режим работы модуля UART как с этим самым половинным стоп-битом, так и с более распространёнными количествами стоп-битов. А мост FT232R не только не способен поддерживать половинный стоп-бит, но также не способен поддерживать полуторный стоп-бит: только один или два стоп-бита.

Или в описании структуры DCB говорится, что значащих бит в одном символе UART может быть от 5 до 8 штук (в это количество не входит бит чётности). А уже упомянутый мост FT232R способен работать только с 7 или 8 битами. Однако, другой похожий на UART стандарт — MDB («Multi-Drop Bus») — содержит, по сути, 9 значащих бит (8 бит данных, плюс бит режима/направления). И микроконтроллер STM32F103 способен работать как с MDB, так и с 8-битным UART.

Теперь, если мы возьмём материнскую плату или преобразователь USB-RS232, вроде «UPort 1115», мы сможем сказать «где-то там есть RS-232». Однако, если мы возьмём микросхему-мост USB-UART с уровнями на линиях RX/TX равными +3,3/0 В, сложится парадоксальная ситуация: описываемые в TIA/EIA-232-F напряжения нигде не соблюдаются, а протокол, реализуемый этим мостом не описан в самом стандарте. То есть RS-232, упоминаемый в подобном контексте, приобретает некоторые постмодернистские черты симулякра — символа, у которого нет оригинала

Возможно также соединить линии USB напрямую к ПЛИС и наделить ПЛИС функционалом, позволяющим ей опознаваться компьютером как USB-устройство класса CDC («Communication Device Class») — то есть как com-порт. Однако, тратить (и в весьма большом количестве!) логические элементы ПЛИС на столь обыденную задачу, реализованную в готовых микросхемах USB-UART имеет смысл только в рамках учебных задач, связанных с изучением протокола USB.

Работа над ошибками

Рассматривая аспекты, связанные с ошибками, возникающими при передаче данных через UART, можно выделить три группы:

-

нестабильности электрических параметров сигнала

-

нестабильности временных параметров сигнала

-

нарушение в логике приёма/передачи

Обсудим ряд аспектов, связанных с каждой из этих групп.

Мажорирование

Когда речь заходит про аппаратное исправление нестабильности электрических параметров, регулярно произносится слово «мажорирование». То есть многократное (обычно — троекратное) снятие показаний в пределах одного принимаемого бита и последующий выбор в качестве истинного значения принимаемого бита того, которое чаще других встретилось в ходе этих замеров.

На первый взгляд, подобный механизм может показаться «серебряной пулей», сводящей вероятность ошибок практически к нулю. Попробуем, однако, оценить количественно степень влияния мажорирования на уровень ошибок.

Немного формул

Предположим, что ошибки в ходе замеров являются независимыми друг от друга и появляются с вероятностью «p». Выпишем в таблицу все 8 возможных комбинаций 3-битного числа. Но вместо единиц в ячейках таблицы запишем вероятность ошибки в конкретном замере («p»), а вместо нулей — вероятность верного считывания («1-p»). Вероятность появления каждой комбинации будет равна произведению содержимого ячеек соответствующего столбца. Поэтому отметим те комбинации, которые всё же приведут к ошибочному считыванию бита при мажорировании, определим вероятности появления этих комбинаций и сложим их всех.

Как видно, вероятность ошибки при мажорировании будет равна:

Или, если раскрыть скобки и упростить выражение, то:

Пока что влияние мажорирования может просматриваться не слишком явно. Для более чёткой картины возьмём десятичный логарифм «pmaj»:

Преобразуем это выражение. Для начала вынесем за скобки логарифмируемого выражения квадрат «p»:

Затем заменим произведение логарифмируемого выражение на сумму логарифмов:

С уменьшением «p», второе слагаемое (второй логарифм) достаточно быстро будет стремиться к десятичному логарифму трёх, который равен 0,477 (так, при «p» равном 10-2 (одна ошибка на сто бит) это слагаемое уже будет равно 0,474).

Иными словами, если вероятность ошибки равна:

…то вероятность ошибки с использованием мажорирования по трём замерам приблизительно равна:

Здесь «x» по идее должен принимать значения от «0» до «-∞», но при приближении к нулю (то есть при приближении «p» к единице) начнут сказываться допущения. Однако уже при «x», равном «-1» (то есть одна ошибка на десять бит), приближённые значения будут отличаться от точных значений всего на 2%.

Представим, что происходит передача данных по UART с конфигурацией «старт‑бит/8 бит данных/стоп‑бит» на скорости 9600 бит/с и «p» равно 10-6. Это означает, что одна ошибка происходит в среднем один раз в две минуты (130 секунд, если точнее). Поиск причины ошибки, появление которой видится квази-случайным и происходит раз в несколько минут, является достаточно неприятным и трудозатратным занятием. Если же мы применим мажорирование, то ошибка, в теории, начнёт возникать с вероятностью 10-11,523. Или приблизительно один раз в 16,5 месяцев. Вроде бы отличный результат.

Однако, что если «p» равно 10-4 ? Что если ошибка происходит один раз в секунду (1,3 секунды, если точнее), но инженер принял решение не кропотливо настраивать различные условия захвата в цифровом осциллографе с целью выявления причин ошибки, а применить мажорирование, и оно сработало идеальным образом?

Тогда «pmaj» будет равно 10-7,523. Или приблизительно один раз в 72 минуты — как раз достаточно, чтобы в случае претензий сказать: «Ну и где? Где эта ошибка? Вот, всё же работает! А вы говорите!» и убыть в закат

Кроме того, предположение о том, что ошибки в различных замерах одного бита являются независимыми не совсем верно. Предположим, что ошибка при считывании очередного бита появляется из-за наводки, скачка в цепи питания, либо чего-то подобного. Если мажорирование не применяется, вероятность ошибки «p» тогда будет равна произведению вероятности возникновения помехи «pnoise» на отношение длительности помехи «tnoise» к длительности бита «T»:

Одинаковую вероятность ошибки может создать как длительная, но редкая помеха, так и короткая, но часто повторяющаяся помеха. Однако, часто повторяющуюся помеху («pnoise» которой много больше, чем собственно «p») будет легче обнаружить, проанализировать и выявить её источник. А редко повторяющаяся помеха, та, от поиска которой, по идее, и должно защитить мажорирование, будет длительной помехой, способной в ряде случаев «накрыть» сразу несколько замеров.

В общем, методы коррекции ошибок, применяемые бездумно, способны как решить проблему, так и в отдельных случаях оказаться заметанием мусора под ковёр или вообще не сработать.

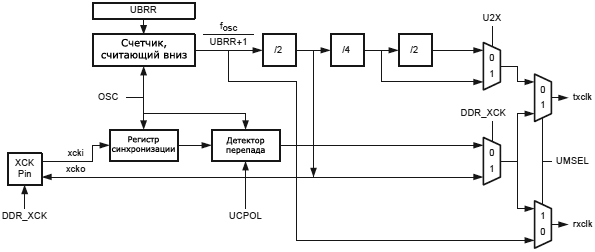

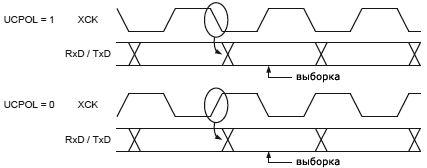

Оверсемплинг

Представим, к примеру, ардуиновский микроконтроллер ATmega328P. В нём битрейт модуля USART задаётся при помощи делителя «UBRR» (он записывается в регистры «UBRRnL» и «UBRRnH») и равен:

Допустим, частота fOSC равна 10 МГц, а нам требуется получить стандартные 9600 бит/с. Тогда наиболее подходящим значением UBRR будет «64». Благодаря ему удастся задать битрейт, равный 9615,4 бит/с. Погрешность в 0,16% кажется незначительной, однако она накапливается с каждым битом. И для последнего фронта в символе составит 1,44%.

Точность внутреннего RC-генератора для того же микроконтроллера ATmega328P при фиксированной температуре в 25°C и напряжении 3,0 В заявлена ±2%. Во всём диапазоне рабочих температур и напряжений заявленная точность генератора падает до крайне грубых ±14%. Но ниже мы будем отталкиваться от первой цифры.

Нестабильность генератора создаёт дополнительную погрешность, которая хоть и не накапливается с каждым битом, но в конце символа способна сложиться с одним и тем же знаком с погрешностью от деления частоты. При этом, суммарная погрешность передатчика может удлинить передаваемые им биты, а суммарная погрешность приёмника — укоротить считываемые им биты. То есть, по сути, погрешности сложатся по модулю.

Если считывание производится непосредственно с частотой битрейта, то рано или поздно возникнет ситуация, когда принимающее устройство зафиксирует появление старт-бита не в середине бита, а в самом его начале (сразу после появления нисходящего фронта) или же в самом конце (перед первым битом данных). Причём сколь угодно близко к фронту. И к последнему биту символа приёмник гарантированно рассогласуется с передатчиком.

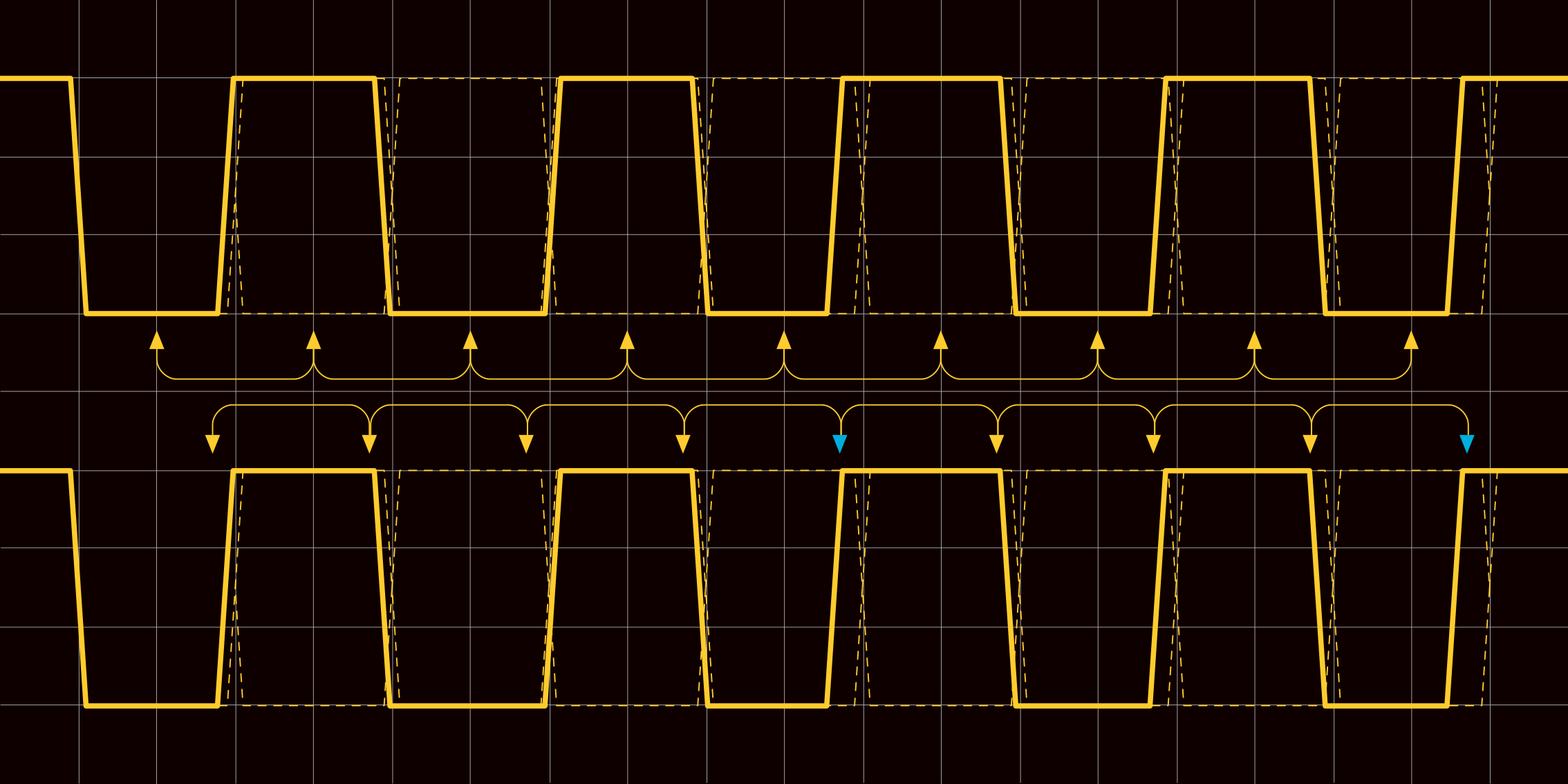

Решением этой проблемы является многократное считывание логического состояния на линии RX — оверсемплинг. После первого считывания, результат которого может быть принят за старт-бит, приёмник ожидает половину битового периода и только начиная с этого момента приступает к считыванию бит через равные промежутки времени. При четырёхкратном чтении, ошибки передачи будут отсутствовать при общей временно́й погрешности, доходящей до 25%!

На этом месте может возникнуть пара вопросов:

-

Какова временная погрешность приёмопередатчиков UART в реальных устройствах?

-

Если приёмник всё равно производит многократное чтение одного и того же бита, возможно ли получаемые данные эффективно использовать также для мажорирования?

Отвечая на первый вопрос, можно обратиться к документу «Determining Clock Accuracy Requirements for UART Communications», выпущенный компанией Maxim Integrated (на текущий момент она поглощена компанией Analog Devices), который говорит следующее:

It is difficult to quantitatively assess a worst-case acceptable sampling range across a bit’s period. EIA/TIA-232-F does specify a 4% of bit-period maximum slew time for a transmission, but this is difficult to achieve for long runs at 192kbps. But for the purpose of this application note, let us define two data path scenarios. Consider a «nasty» scenario, which can only be sampled reliably within the middle 50% of the bit time. This could equate to a long capacitive RS-232 run. The «normal» scenario can be sampled within the middle 75% of the bit time.

То есть инженеры Maxim Integrated предполагают, что невозможность корректно считать значения на линии RX в течении 25% от длительности бита — это вполне нормальное явление.

Если же проводить тест по маске, к примеру, для платы производства WaveShare с микросхемой FT232RL (с внутренним тактовым генератором) при битрейте 9600 бит/с, то из допуска ±2% от длительности бита последний фронт символа (восходящий фронт стоп-бита) будет «вываливаться» с вероятностью 0,55%. А из допуска ±4% с вероятностью 0,5×10-5 %. Можно предположить, что допуск в 10–12% (±5…6%) будет достаточно широк для того, чтобы считать вероятность выхода из него несущественной величиной. Если происходит обмен данными между двумя устройствами с допуском в 10…12% у каждого, то имеет смысл говорить об общей погрешности как раз в 20…24%.

Для ответа на второй вопрос представим себе, что у нас есть 8-кратный оверсемплинг и 25% общей погрешности, связанной с временными характеристиками. Два семпла окажутся в зоне 25%. Ещё на один семпл попадает «игла», которую мы пытаемся устранить при помощи мажорирования (ведь исправлять помехи имеет смысл только когда они есть, а словосочетание «есть помеха» означает, что помехи попадают по семплам). Итого мы получим 5 годных для мажорирования семплов к которым добавлено 3 гарантированно ненадёжных семпла.

Подобная конструкция не представляется такой уж надёжной. Поэтому, к примеру, в STM32F103 коррекция ошибок (мажорирование по восьмому, девятому и десятому семплам бита), дополнена механизмом сигнализация об их наличии.

То есть если три семпла, взятые посередине бита не равны все нулю или все единице, то такое значение, вообще говоря, не считается действительным.

Ошибки логики

Является ли ошибкой отсутствие стоп-бита? То есть если был передан старт-бит, затем оговоренные N бит данных, а после этого стоп-бит не появился (линия вместо стоп-бита оказалась в состоянии логического нуля)? Не всегда. Так, стандарт «ANSI E1.11», описывающий протокол обмена данными светотехнического оборудования DMX512, похожий на классический UART, использует при передаче данных аналогичное действие. При номинальной длительности бита DMX512 равной 4 мкс, переход в логический ноль и последующее удержание этого состояния в течение 92 мкс (то есть 23 нулевых бита подряд) или более, называется «break» и маркирует начало очередного пакета данных.

Однако, в общем случае, если передаваемый символ состоял не только из нулей, отсутствие стоп-бита будет, пожалуй, именно ошибкой — «framing error».

Является ли ошибкой отсутствие второго стоп-бита, если на стороне компьютера был выбран режим с двумя стоп-битами, а коммуницирующее устройство было настроено на работу с одним стоп-битом?

Пожалуй, нет. Так, в документации на ардуиновский микроконтроллер ATmega328P написано:

The Receiver and Transmitter use the same setting. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter. An FE (Frame Error) will only be detected in cases where the first stop bit is zero.

Ещё более подчёркнуто это написано в документации на упоминавшиеся микроконтроллеры STM32F103:

2 stop bits: Sampling for 2 stop bits is done on the 8th, 9th and 10th samples of the first stop bit. If a framing error is detected during the first stop bit the framing error flag will be set. The second stop bit is not checked for framing error.

Относительно современная микросхема Super-I/O NCT6776D, реализующая UART на материнских платах, косвенно ссылается в своей документации на ставшую де-факто стандартом, классическую микросхему PC16550D:

NSER (No Stop Bit Error). This bit is set to logical 1 to indicate that the received data have no stop bit. In 16550 mode, it indicates the same condition for the data on the top of the FIFO. When the CPU reads USR, it sets this bit to logical 0.

А в документации на микросхему PC16550D написано:

If bit 2 is a logic 0, one Stop bit is generated in the transmitted data. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half Stop bits are generated. If bit 2 is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, two Stop bits are generated. The Receiver checks the first Stop bit only, regardless of the number of Stop bits selected.

Заключение

Типичная схема применения UART — это старт-бит, 8 бит данных и один-единственный стоп-бит. Типичный битрейт — 9600 бит/с (то есть длительность любого бита будет равна 104,17 мкс). В типичном случае «break frame» (большое количество нулевых бит) не применяется и будет просто ошибкой передачи. Так что базово UART относительно прост.

А упомянутые в статье особые случаи являются исключениями. О существовании которых, однако, имеет смысл знать. Также имеет смысл знать о практике применения данного протокола в индустрии. К примеру, посмотреть, какие возможности предоставляют различные микросхемы мостов USB-UART. Их детальный обзор — в следующей статье.